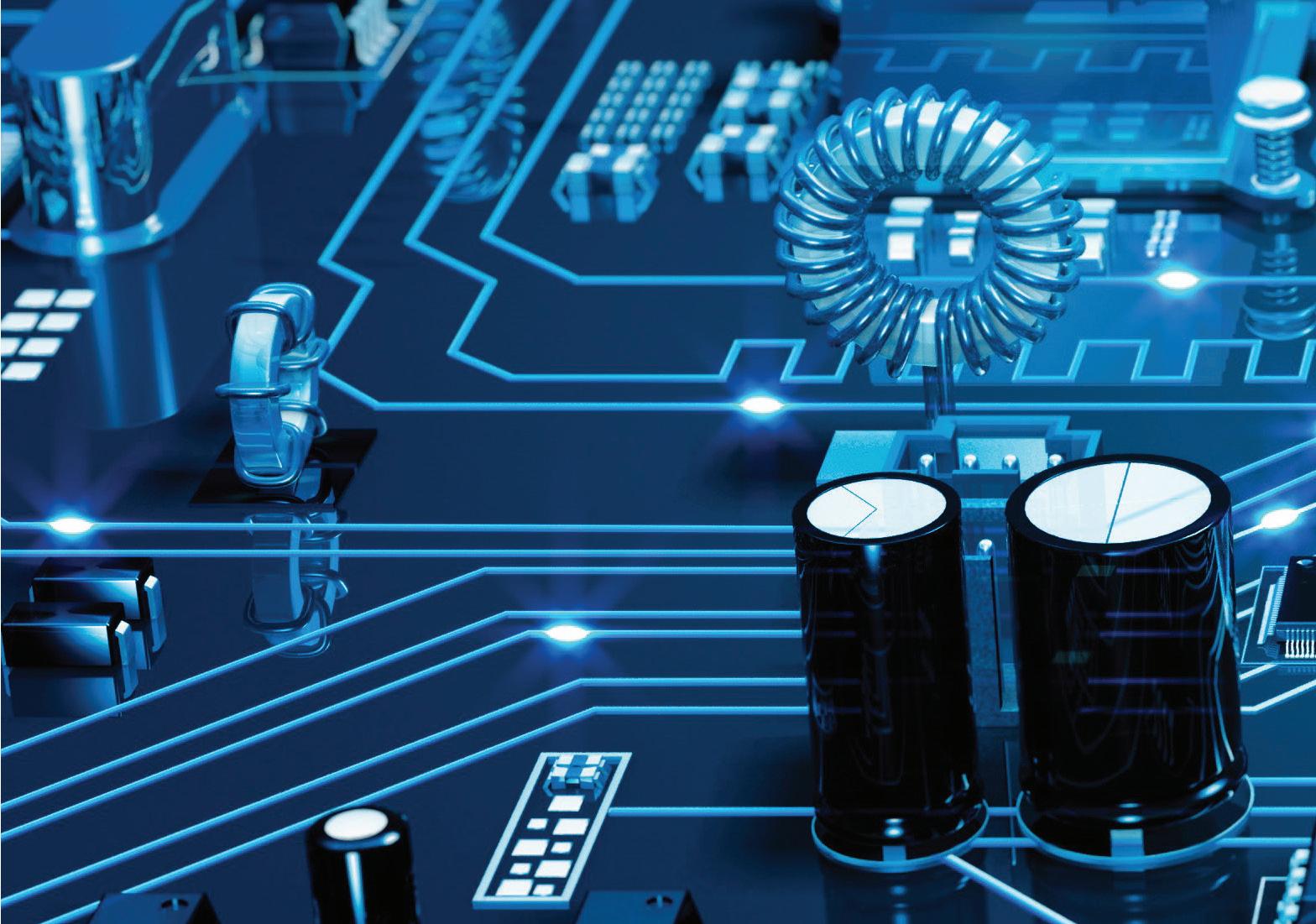

POWER ELECTRONICS HANDBOOK

A SUPPLEMENT TO DESIGN WORLD FEBRUARY 2023 How to control dc microgrids Page 12 Simplifying designs for high power density applications Page 16 Selecting dc-dc converters for railway applications Page 45

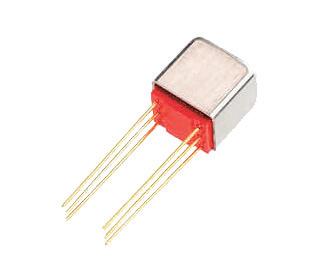

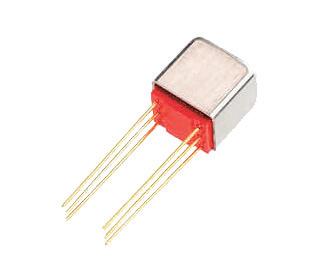

The most demanding applications require the world’s most reliable components. For over 50 years PICO Electronics has been providing innovative COTS and custom solutions for Military, Commercial, Aerospace and Industrial applications. Our innovative miniature and sub-miniature components are unsurpassed in any industry. PICO Electronics’ products are proudly manufactured in the USA and are AS9100D Certified.

To learn more about our products and how you can benefit from our expertise visit our website at picoelectronics.com or call us today at 800-431-1064.

TRANSFORMERS

• Ultra Miniature Designs

• MIL-PRF-27/MIL-PRF-21038

• QPL Approved DSCC

• Audio/Pulse/Power/EMI Multiplex Models Available

• For Critical Applications, Pico Continues to Be the Industry Standard

Surface Mount & Thru Hole Military • COTS • Industrial

• MIL/COTS/Industrial Models

• Regulated/Isolated/Adjustable Programmable Standard Models

• New High Input Voltages to 900VDC

• AS9100D Facility/US Manufactured

• Military Upgrades and Custom Modules Available

VISIT OUR EXCITING NEW WEBSITE: www.picoelectronics.com Transformers & Inductors, DC-DC Converters,AC-DC Power Supplies The big name in miniature components. The big name in miniature components.

CONVERTERS

1-300

DC-DC

2V to 10,000 VDC Outputs —

Watt Modules

& INDUCTORS

Think Pico SmallOver 5000 Std Ultra Miniature

.18" think... ht.

Certified to AS9100D ISO 9001:2015 low

Call Toll Free: 800-431-1064 E Mail: Info@picoelectronics.com • FAX: 914-738-8225 143 Sparks Ave, Pelham, NY 10803 PICO Electronics Inc.

profile from

08 Extended Power Range GaN-based USB-C adapters and chargers deliver increased performance

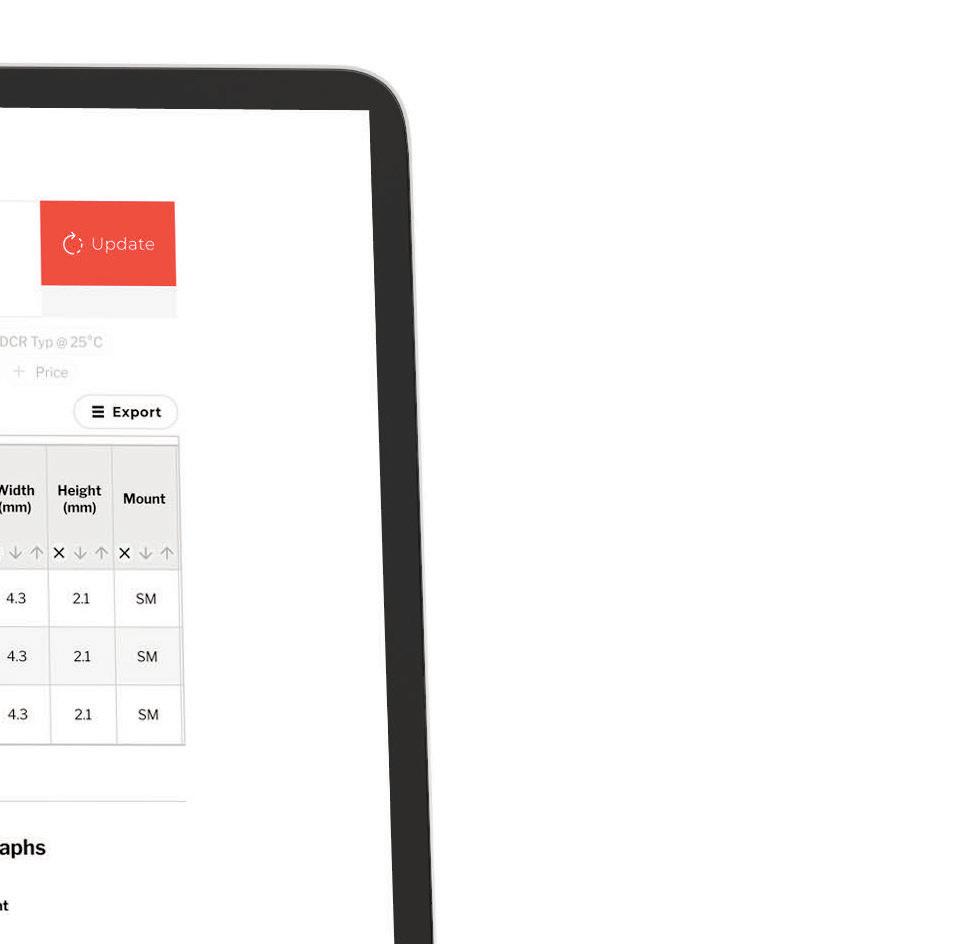

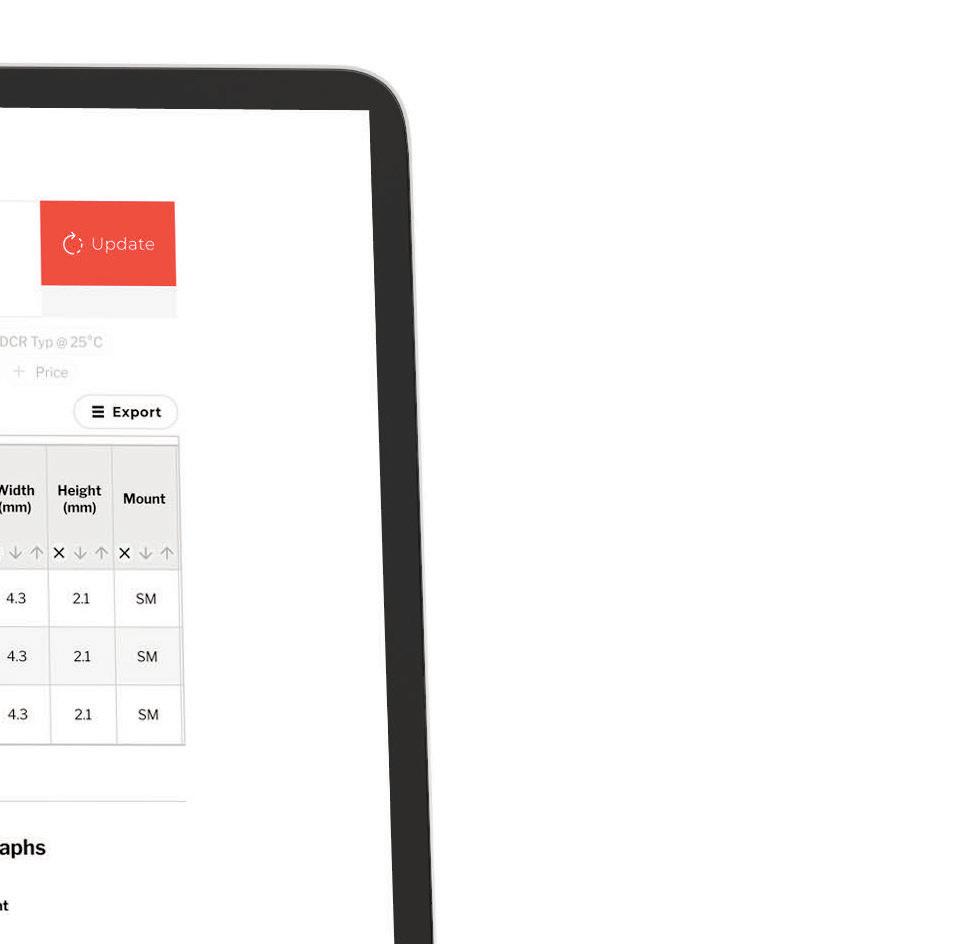

An innovative, highly integrated combo controller for the joint control of the PFC and the hybrid flyback stage.

12

How to control dc microgrids

Microgrids are a great way to power locations where grid connections are unreliable, though it can be tricky to control them in robust ways.

16 Simplifying designs for high power density applications

High-density power module technology for FPGAs, SoCs, & ASICs makes designing easy by providing the highest power densities in the smallest spaces.

20 Power optimization techniques for low-power signal chain applications

Several system-level techniques are available that can make signal chains designs more power efficient and reduce system design complexity.

26 A better way to handle dc-dc converter hold-up times

Converters with built-in holdup circuitry reduce the size and requirements for input capacitors.

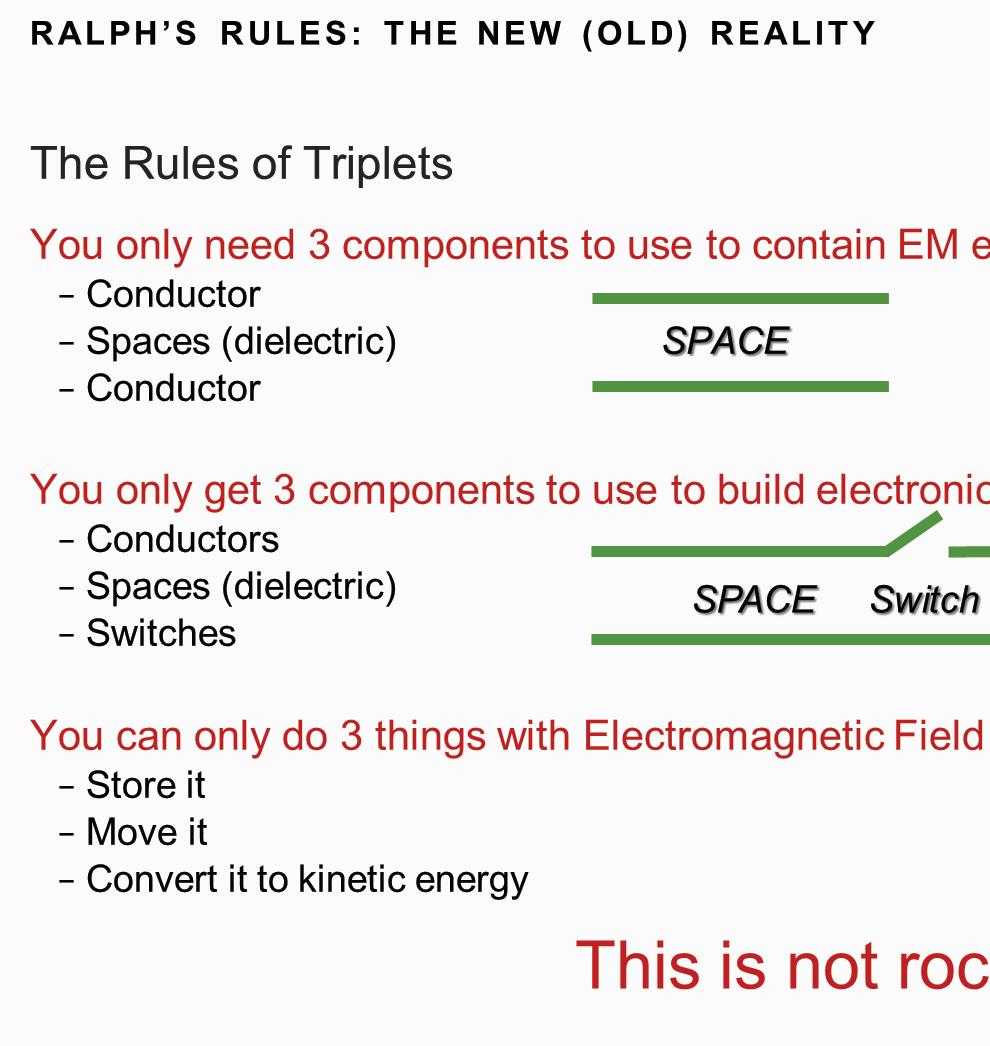

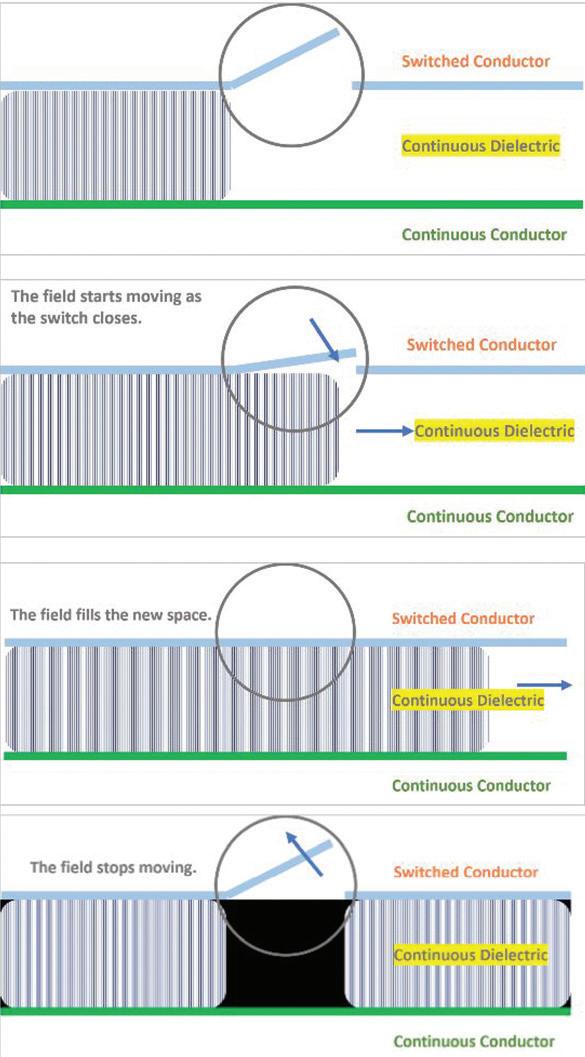

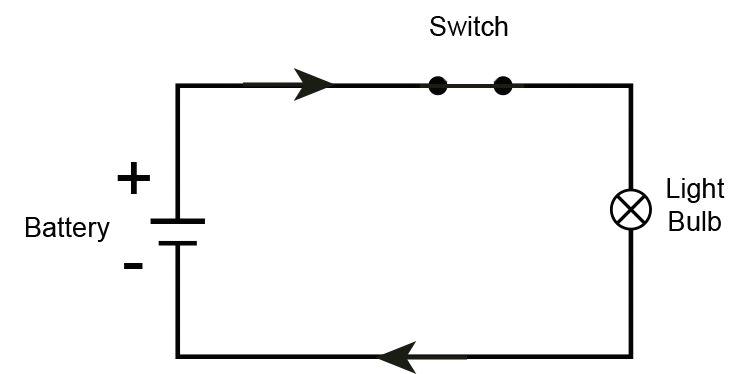

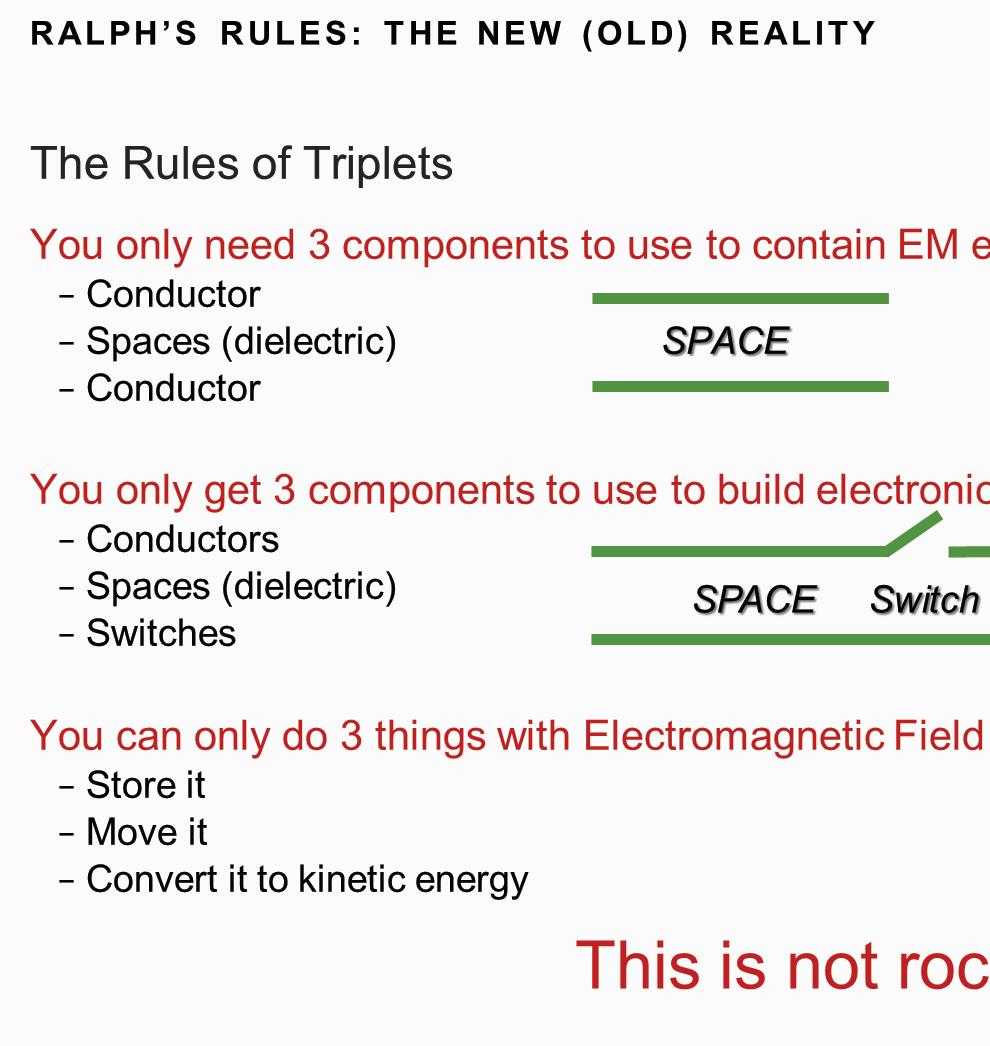

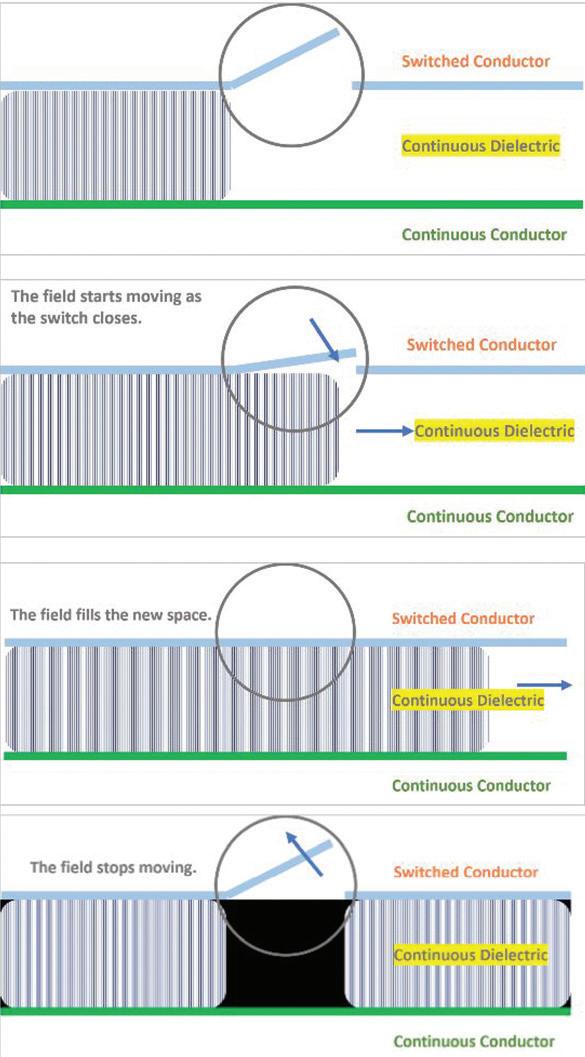

28 Circuit boards don’t behave the way you think they do Circuit designers increasingly must concentrate on the design of transmission lines, or the “spaces” between traces, instead of the

32 The case for AEC-Q semiconductors in non-automotive uses

Specifying parts built in AEC-Q-certified fabs is an inexpensive way of creating exceptionally reliable, long-lasting designs.

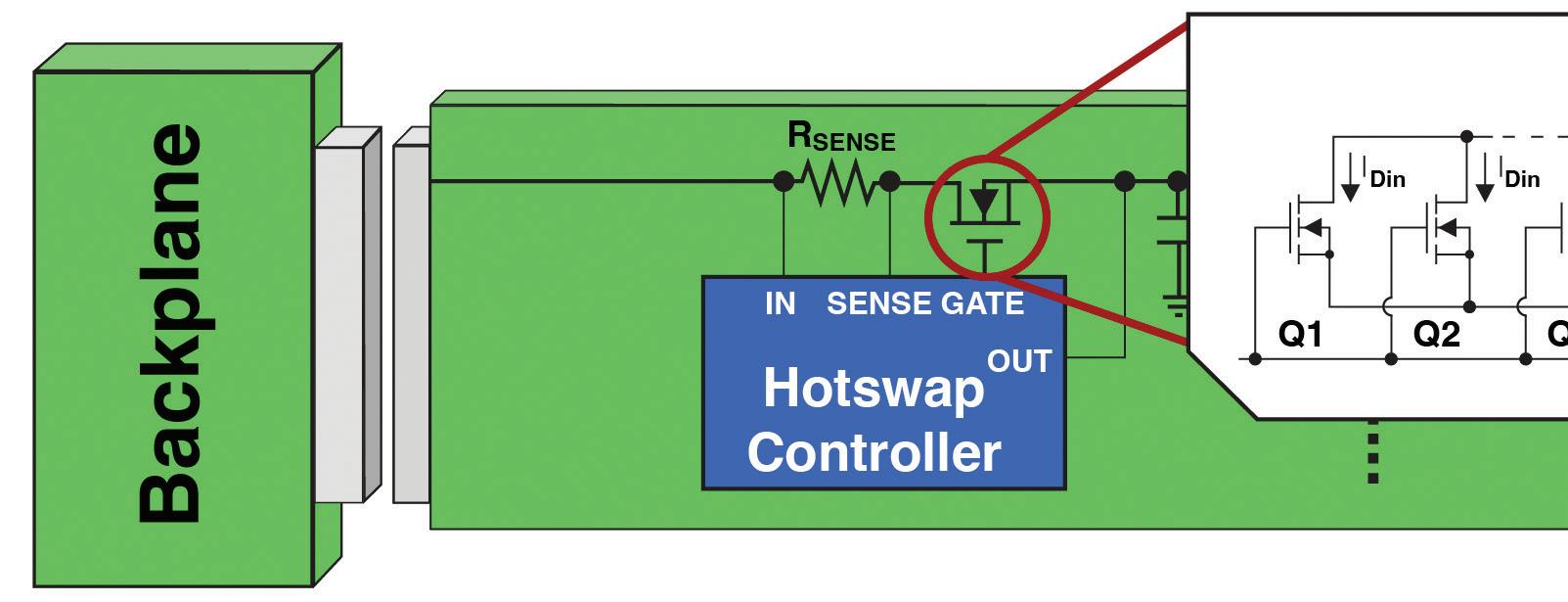

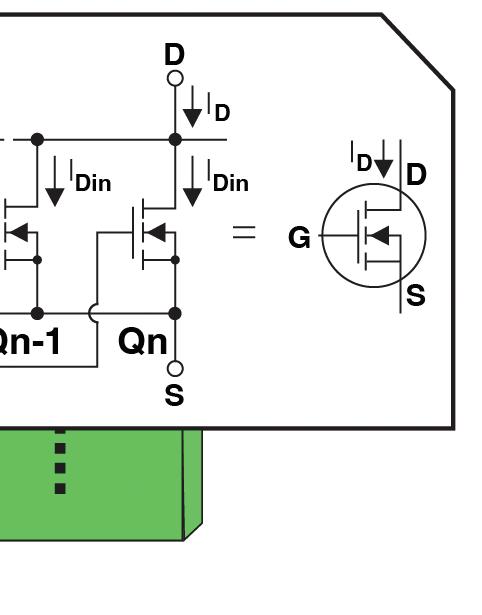

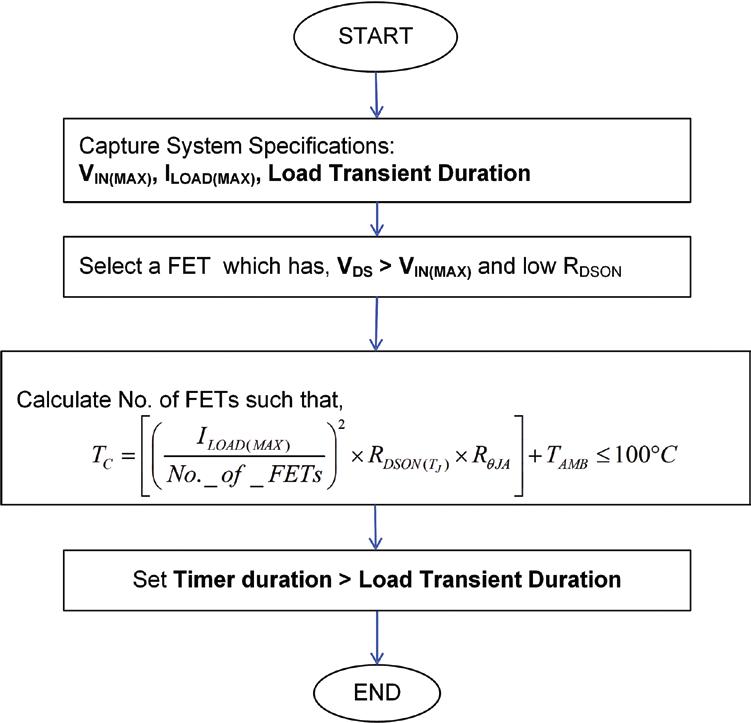

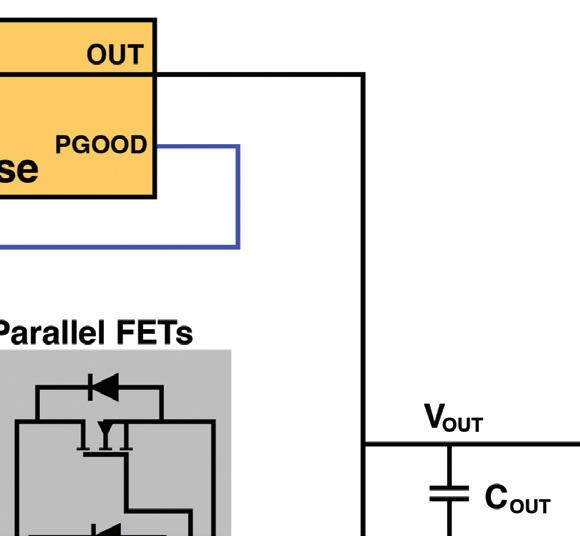

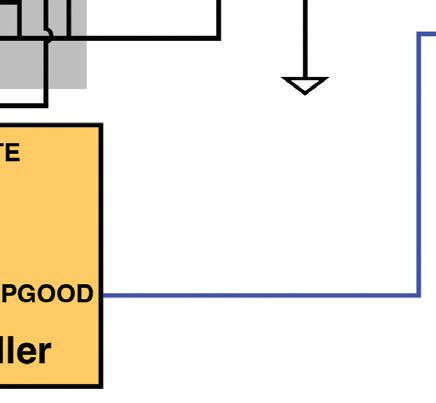

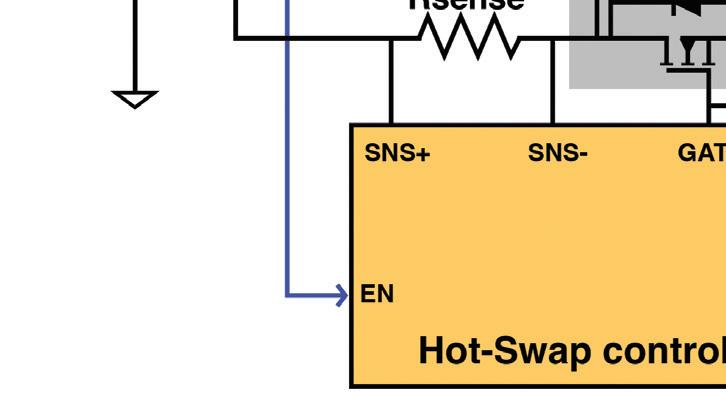

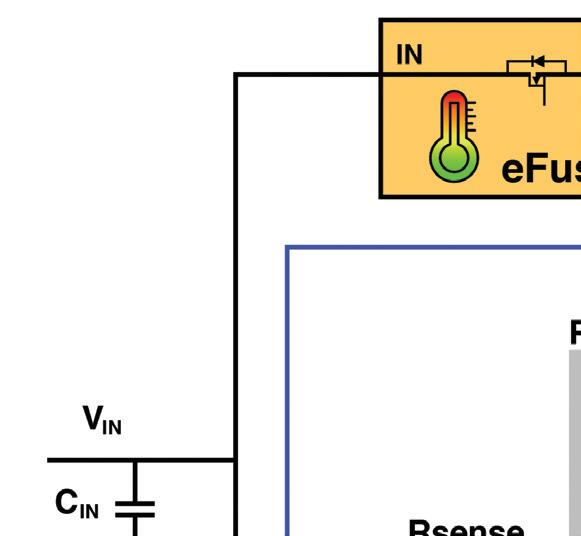

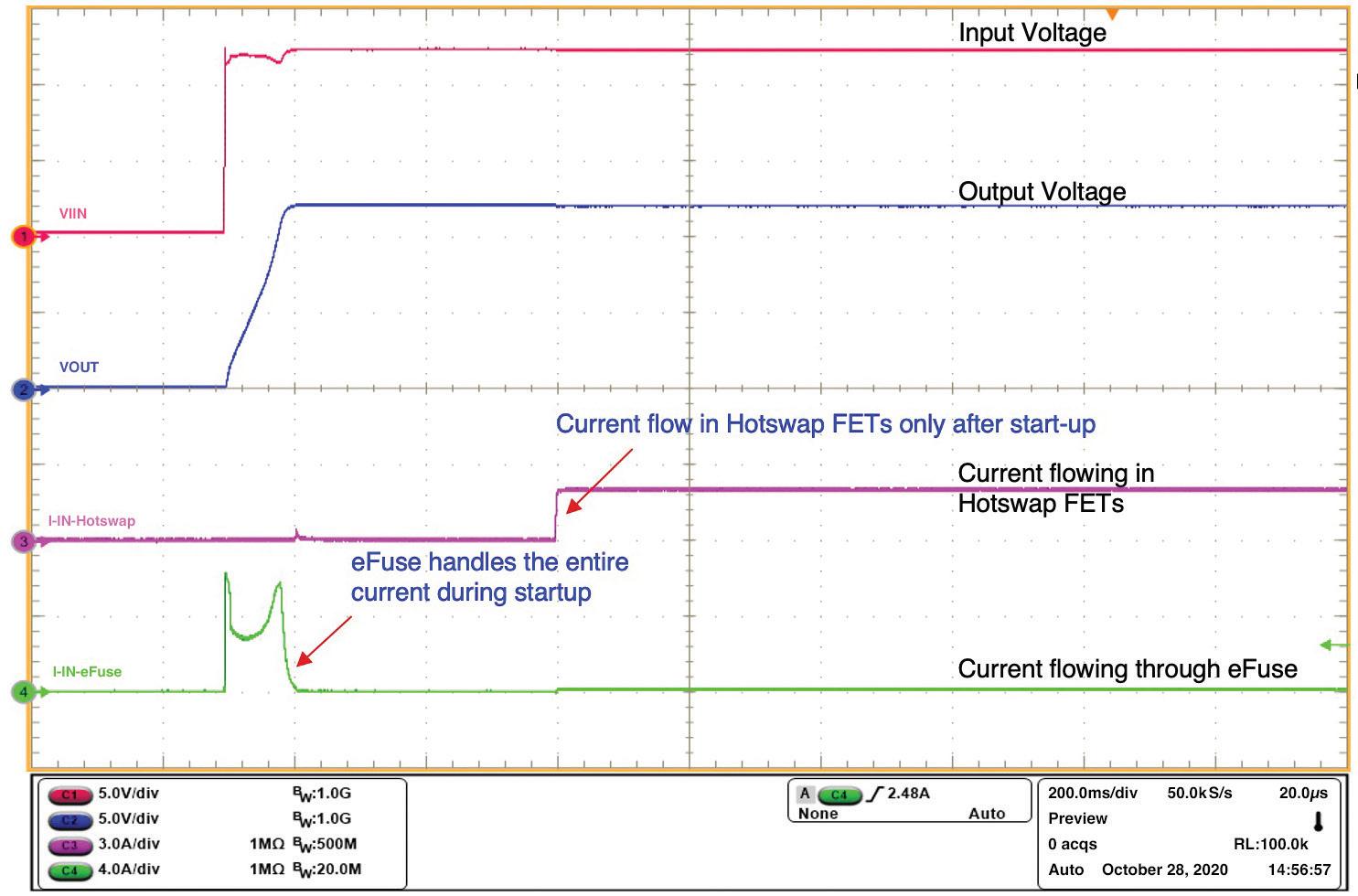

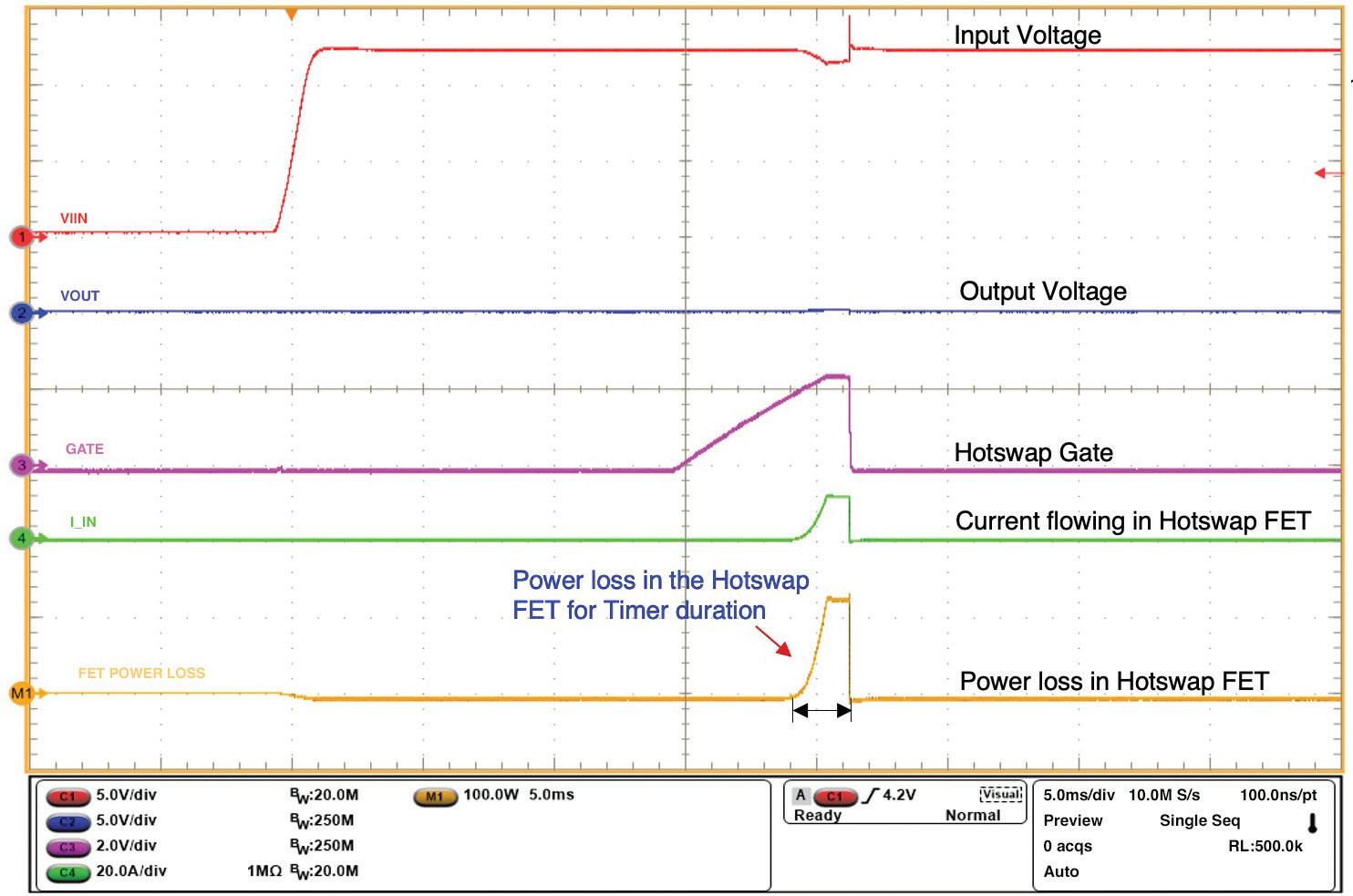

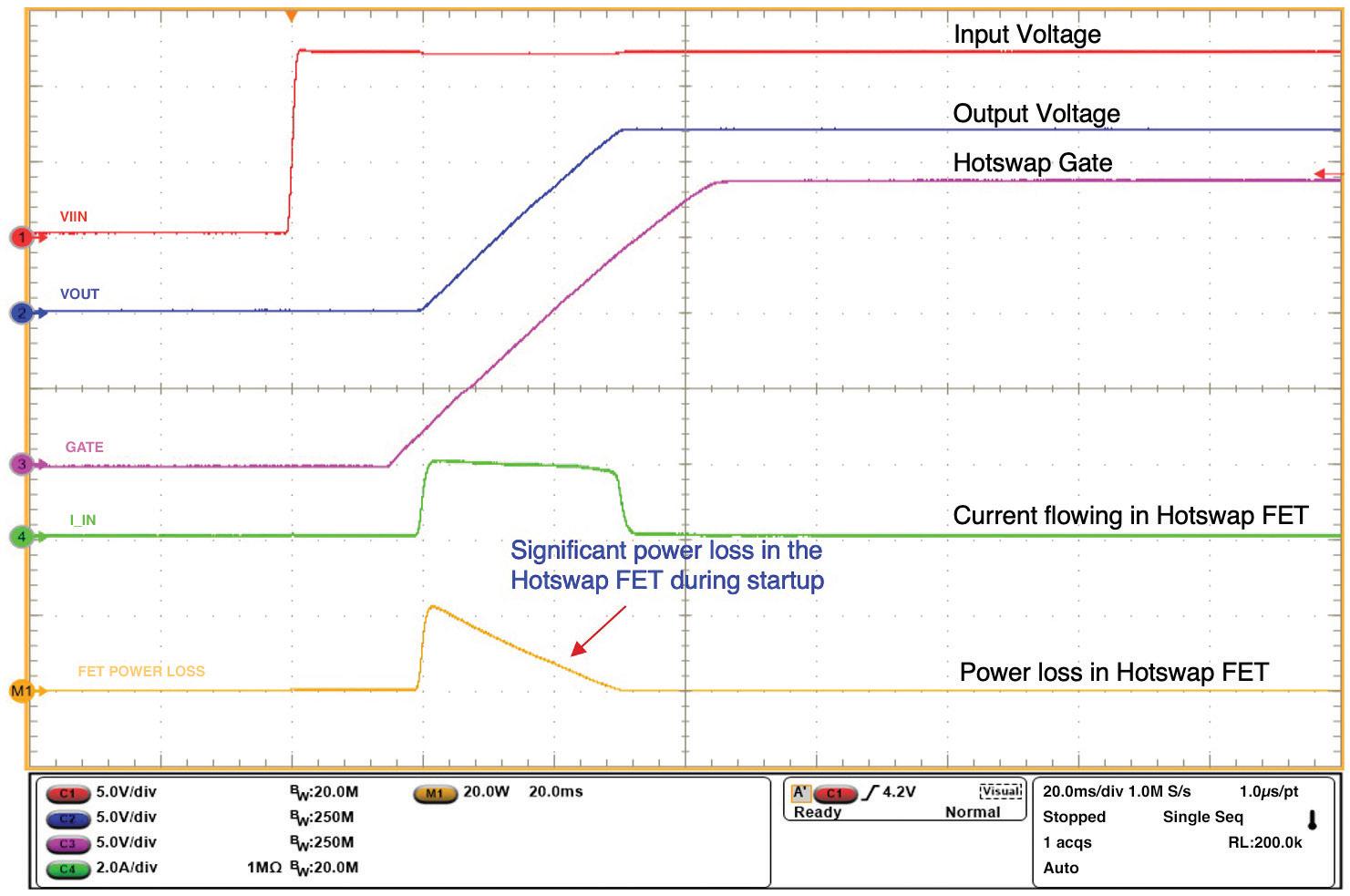

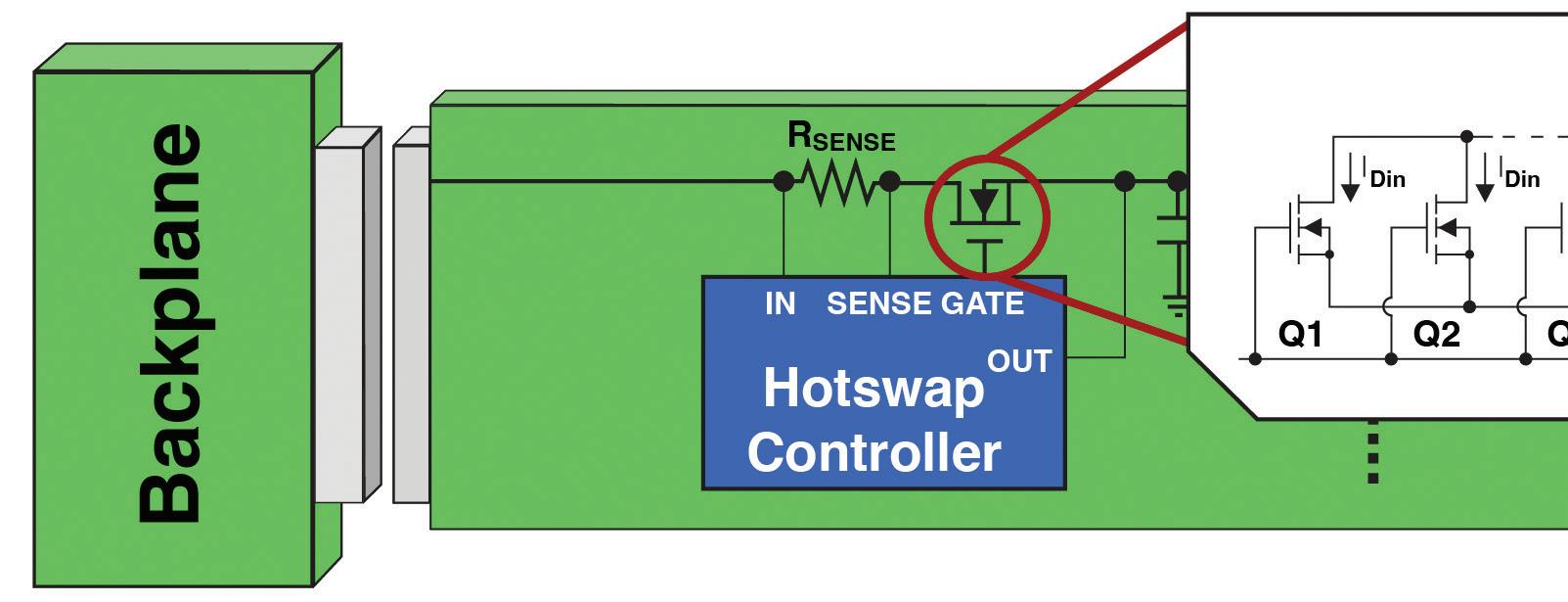

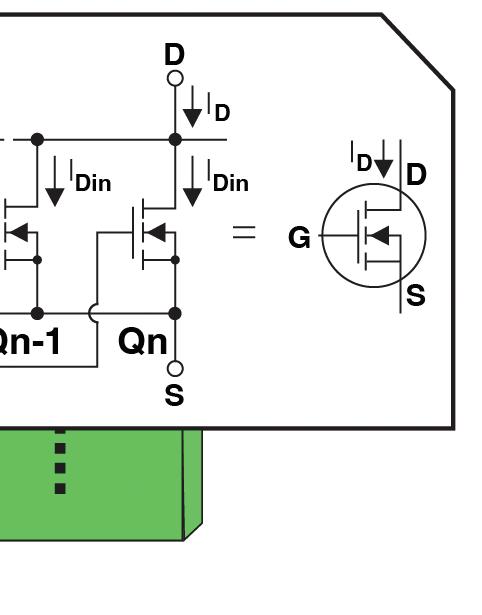

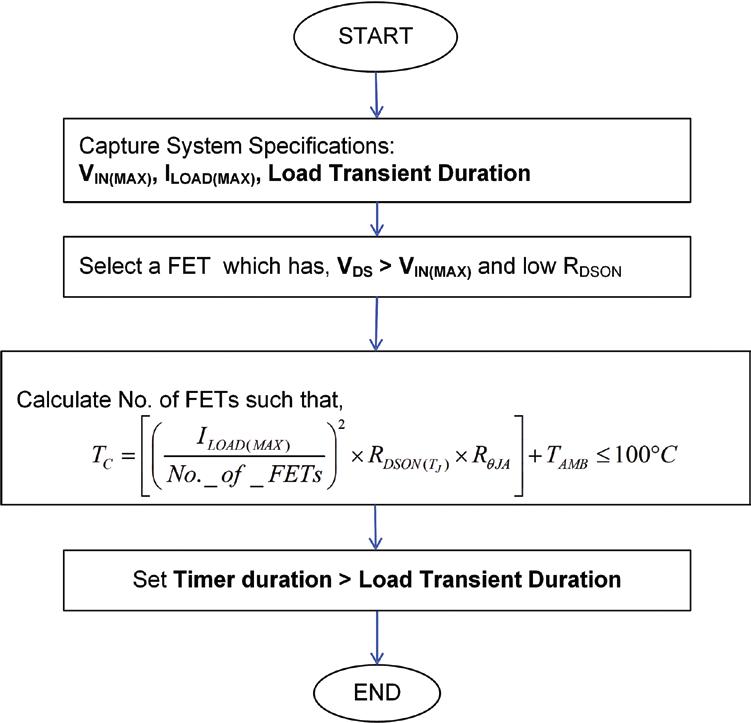

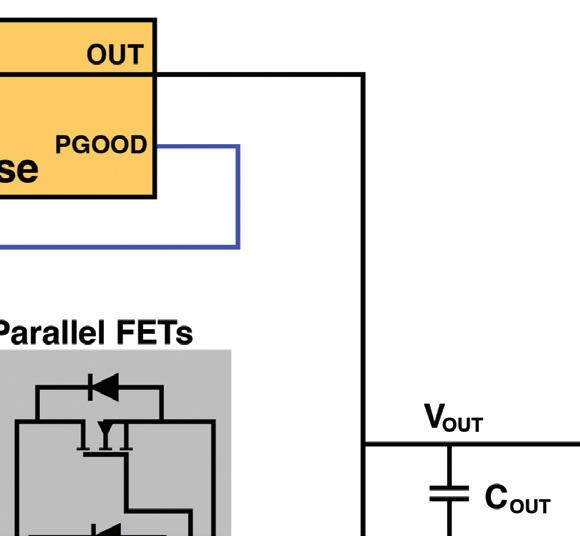

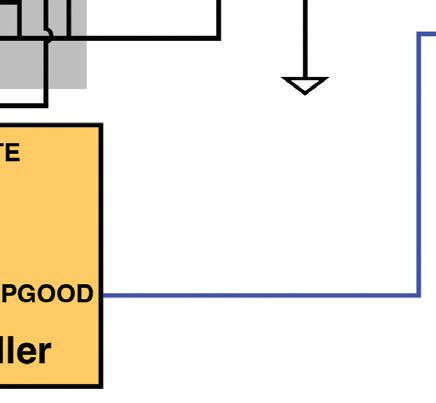

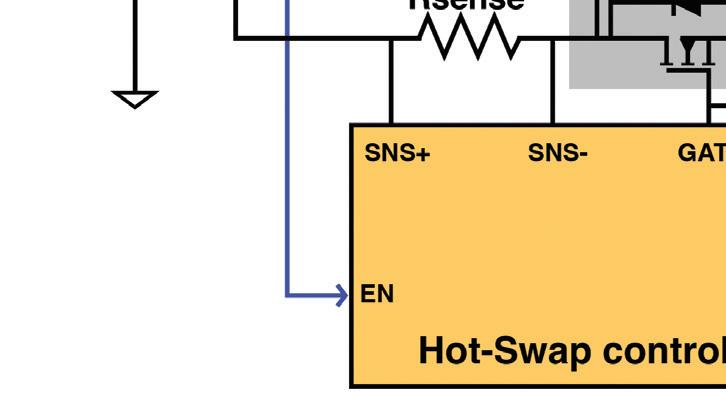

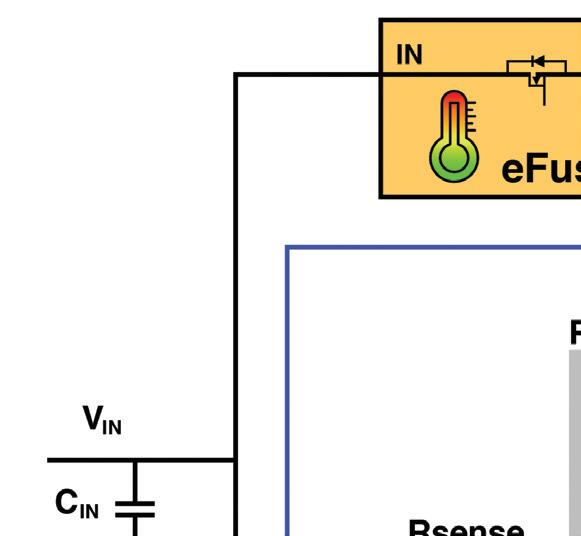

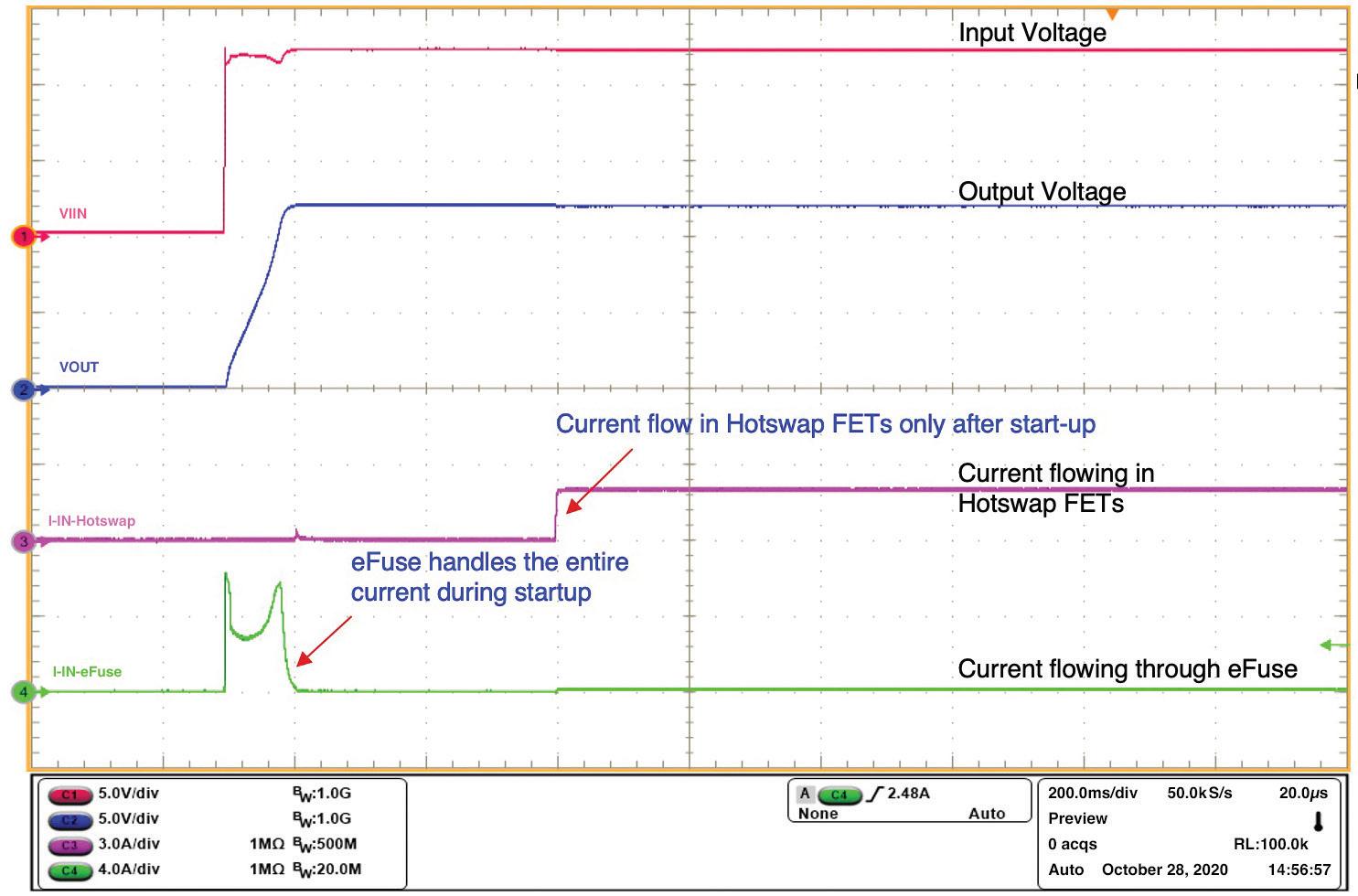

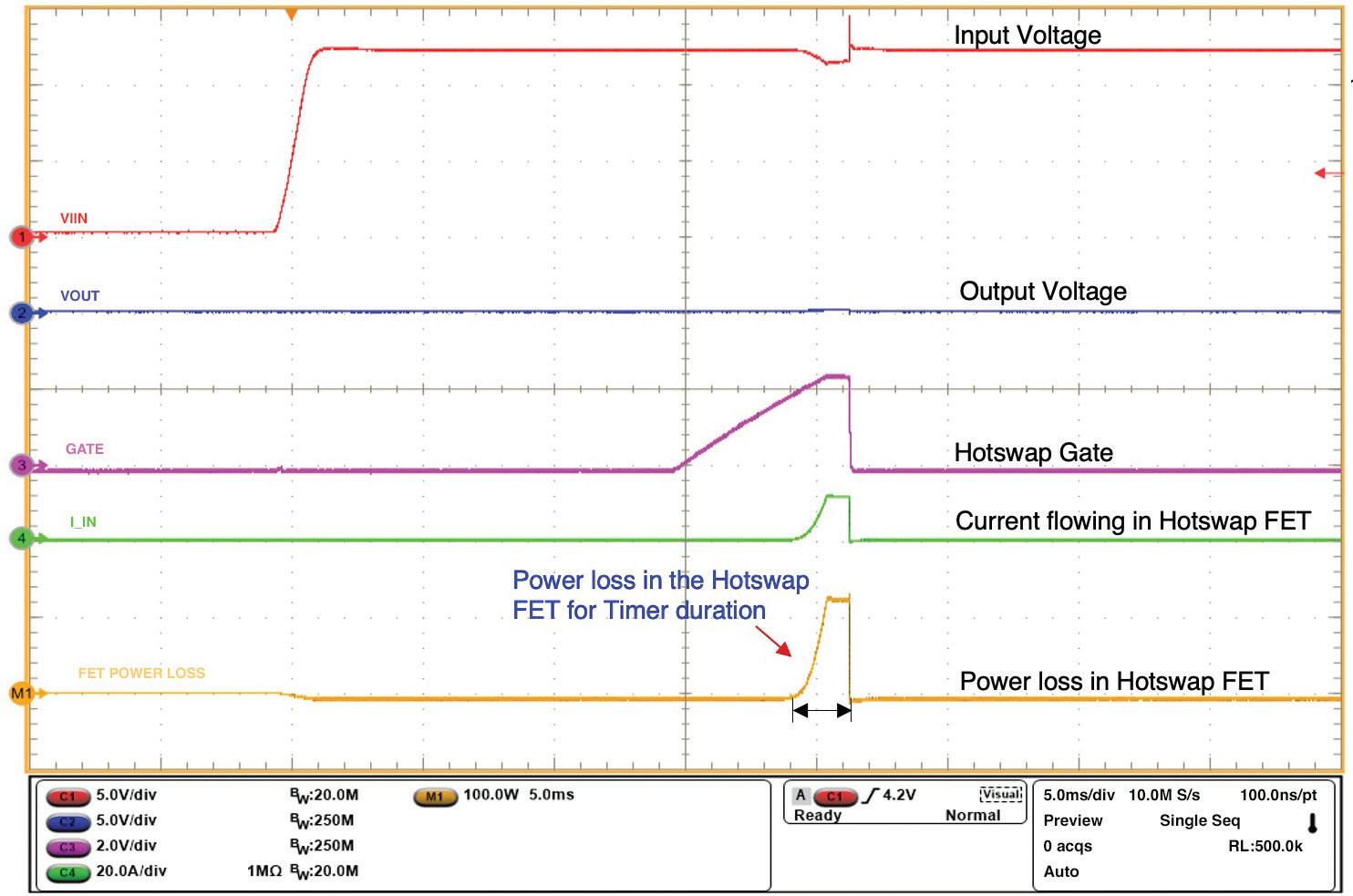

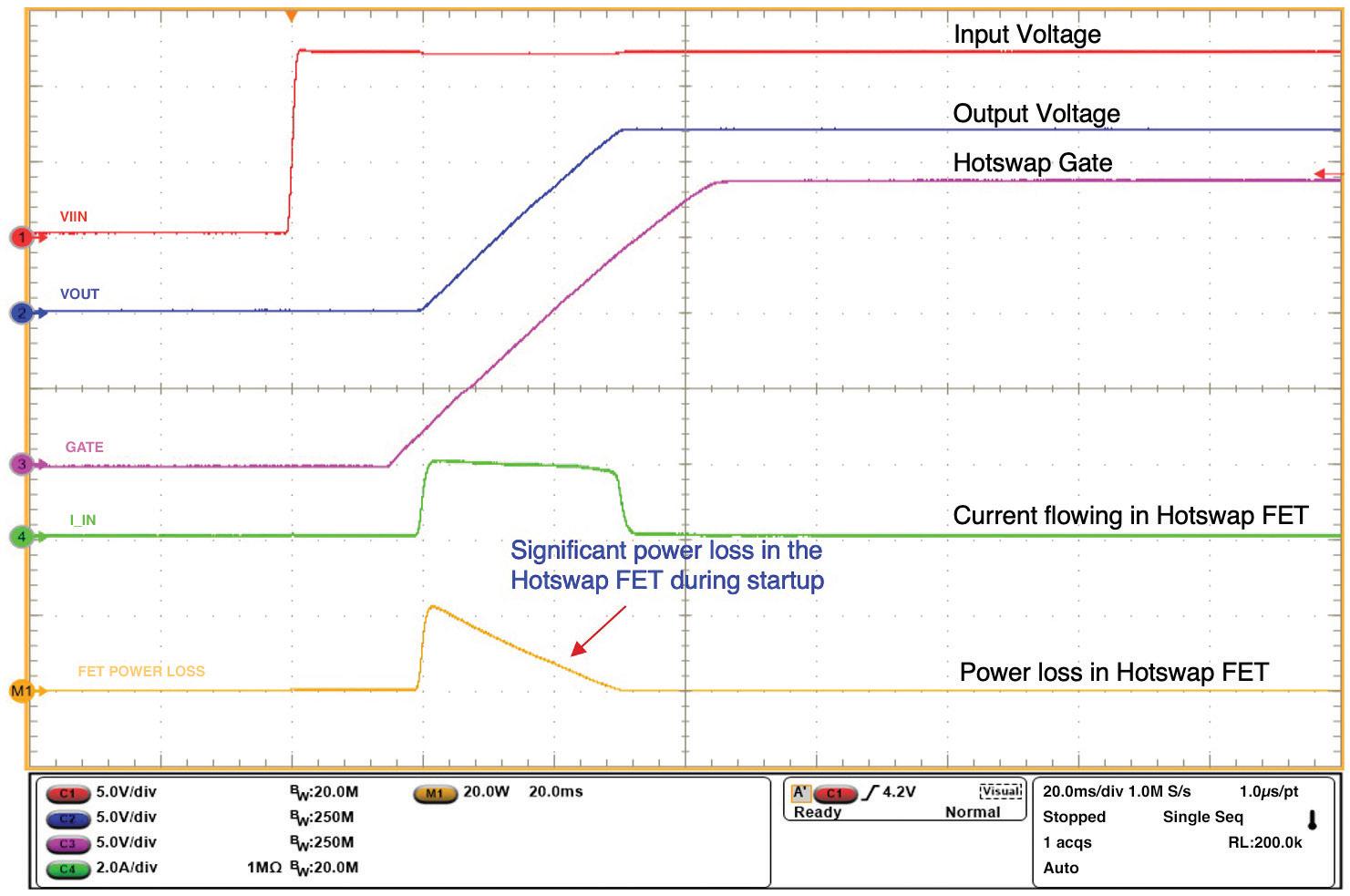

34 Enabling a do-it-yourself hot-swap circuit design using a hybrid architecture

Implementing a hybrid hot-swap circuit can make your life easier by eliminating a complex design process while ensuring robust protection, reduced solution size, and cost.

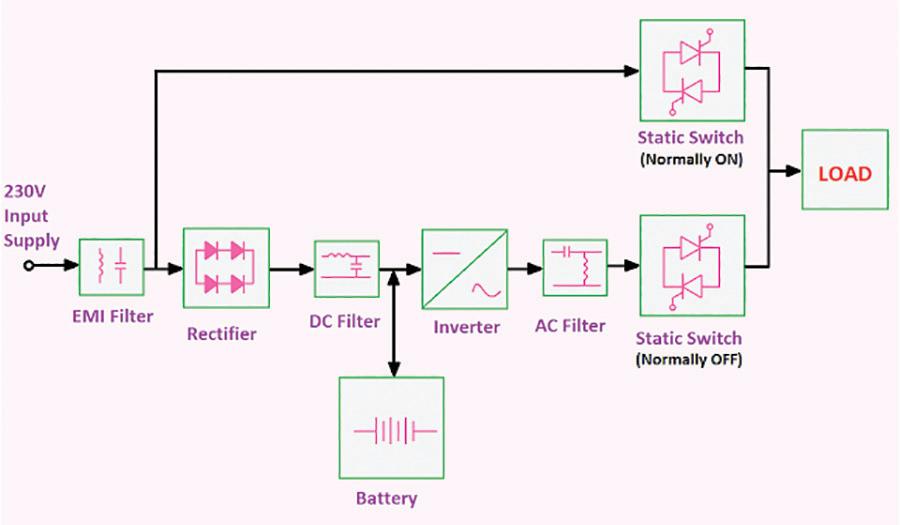

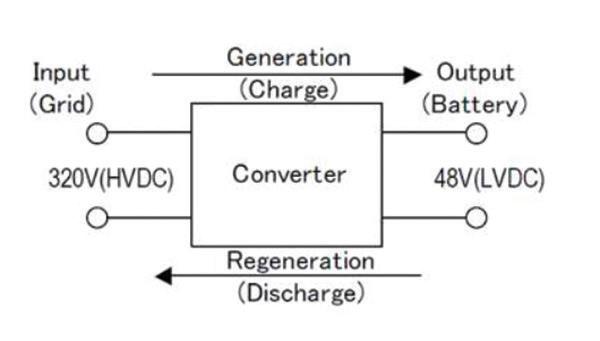

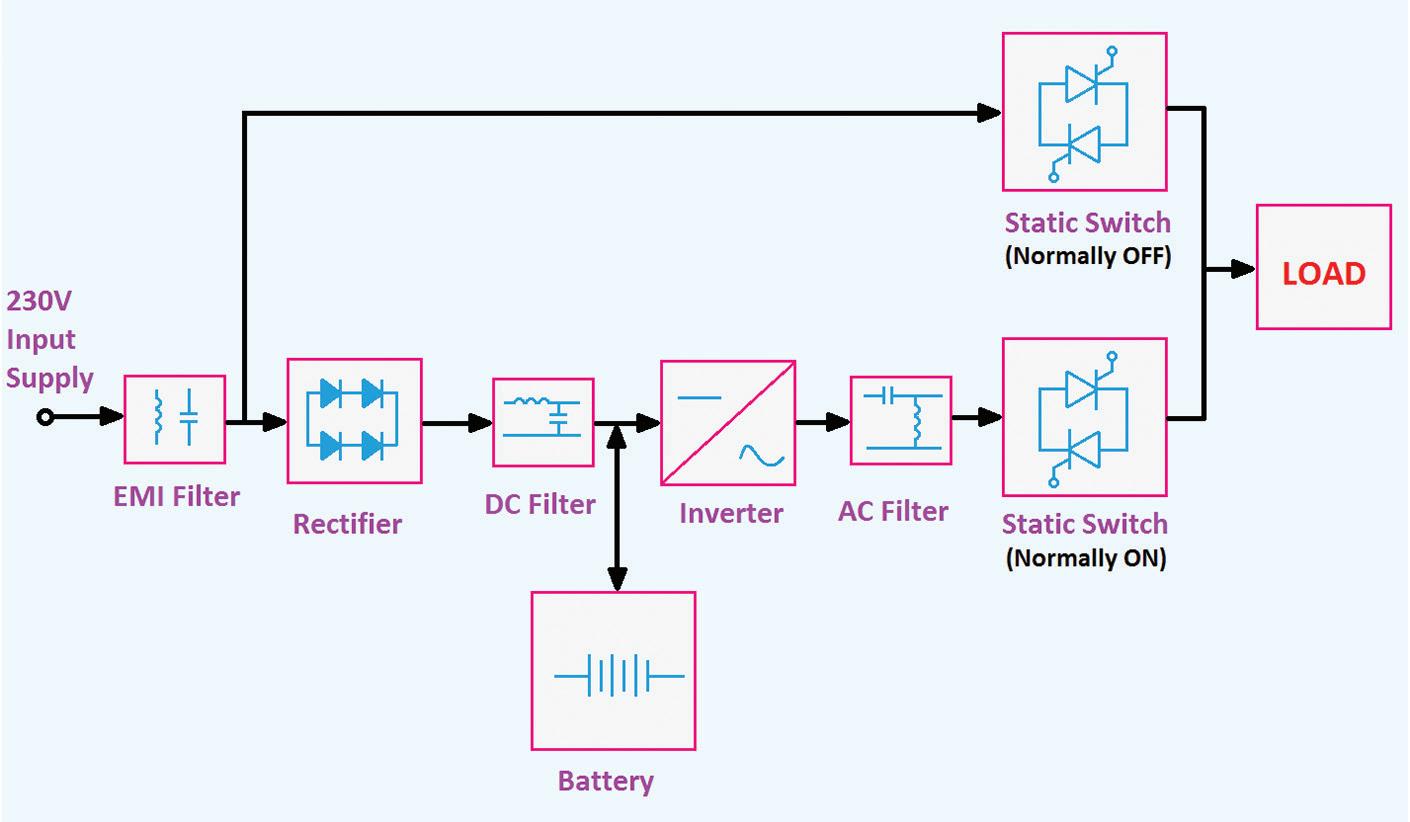

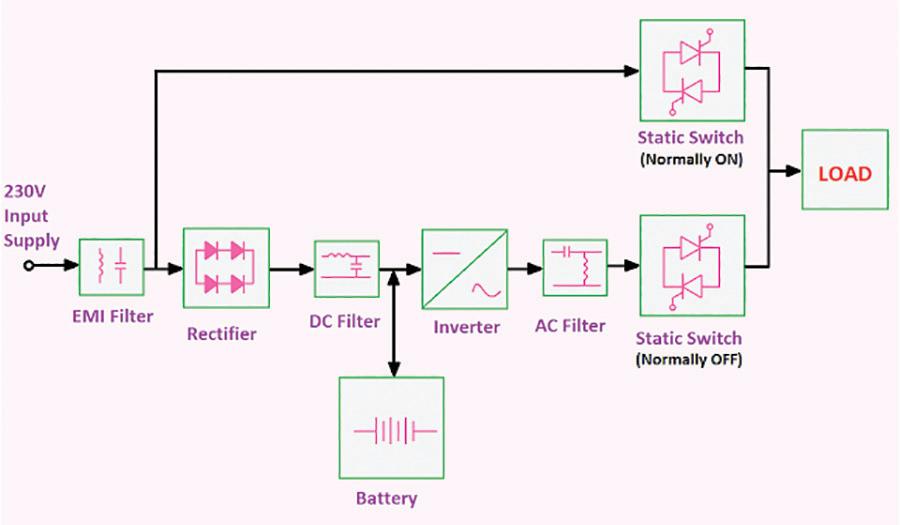

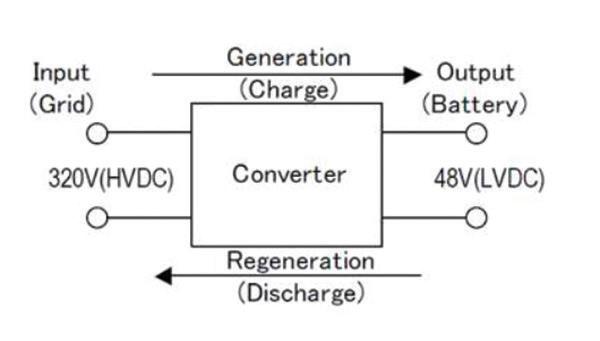

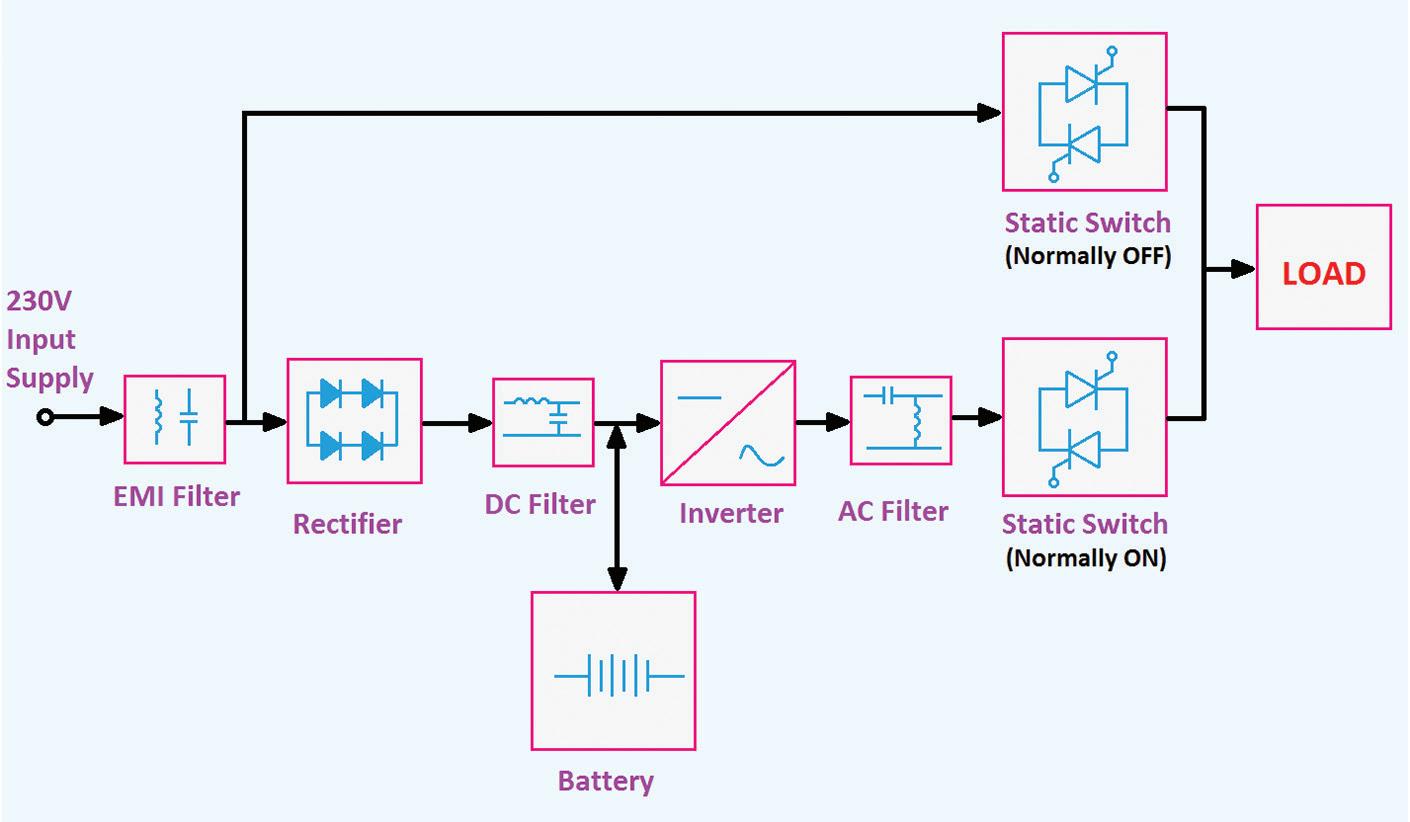

38 Bidirectional power supplies support new UPS requirements

Bidirectional power supplies dynamically direct power from multiple sources to different loads, some of which are also power sources at other times.

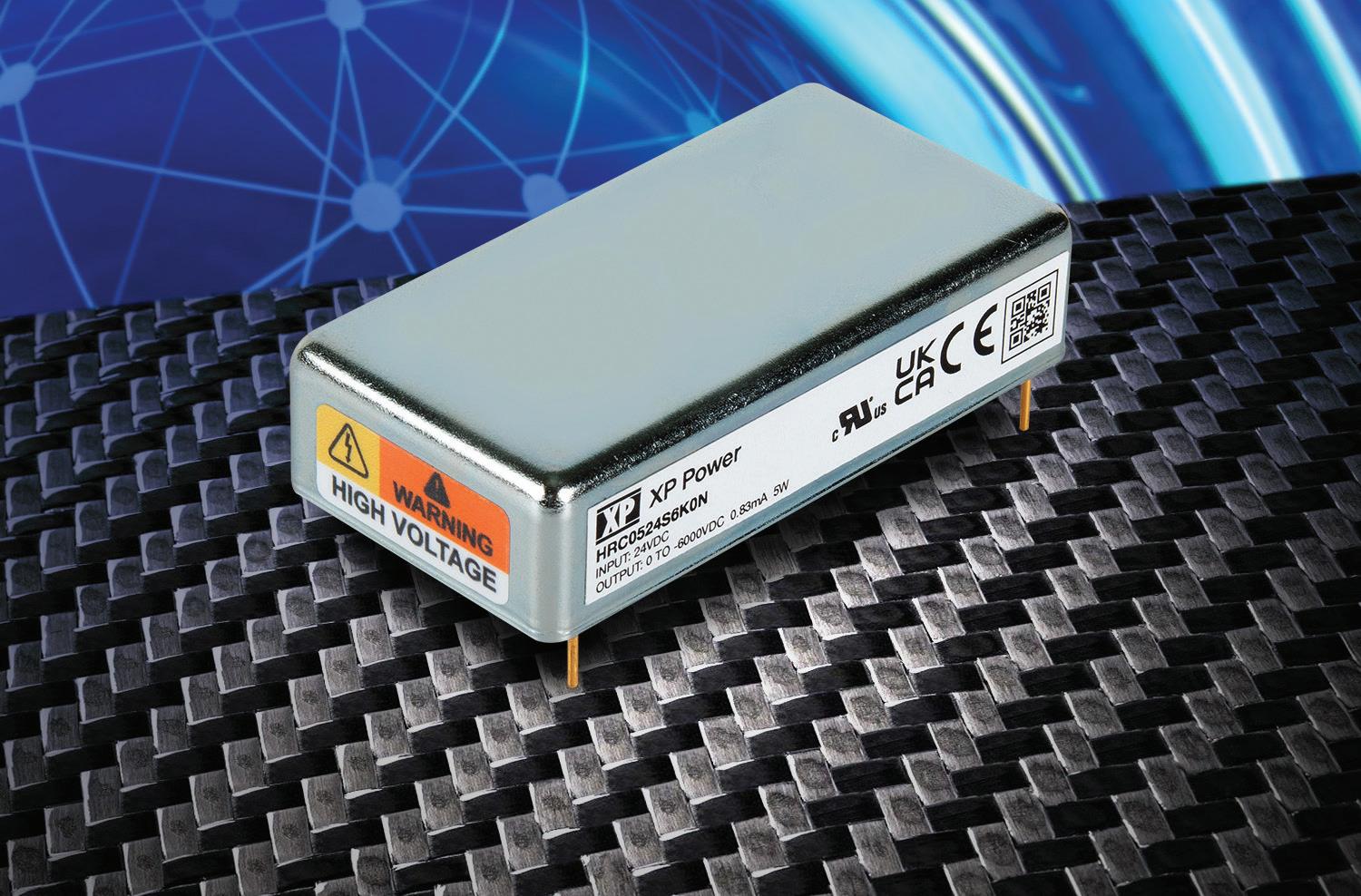

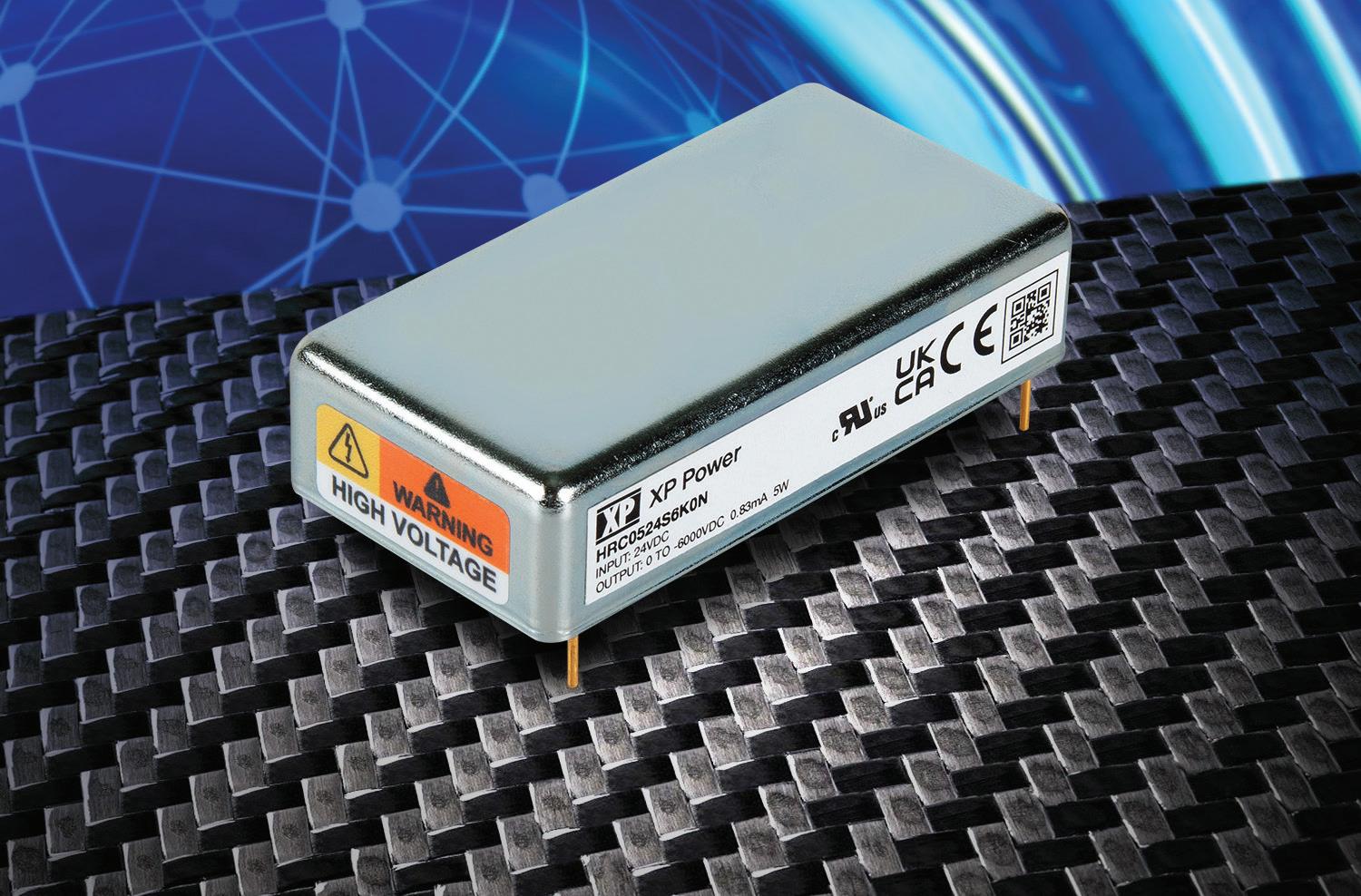

42 Key considerations when integrating high voltage dc-dc converters into critical applications

Knowing precise parameters up front goes a long way to ensuring your critical application meets performance expectations.

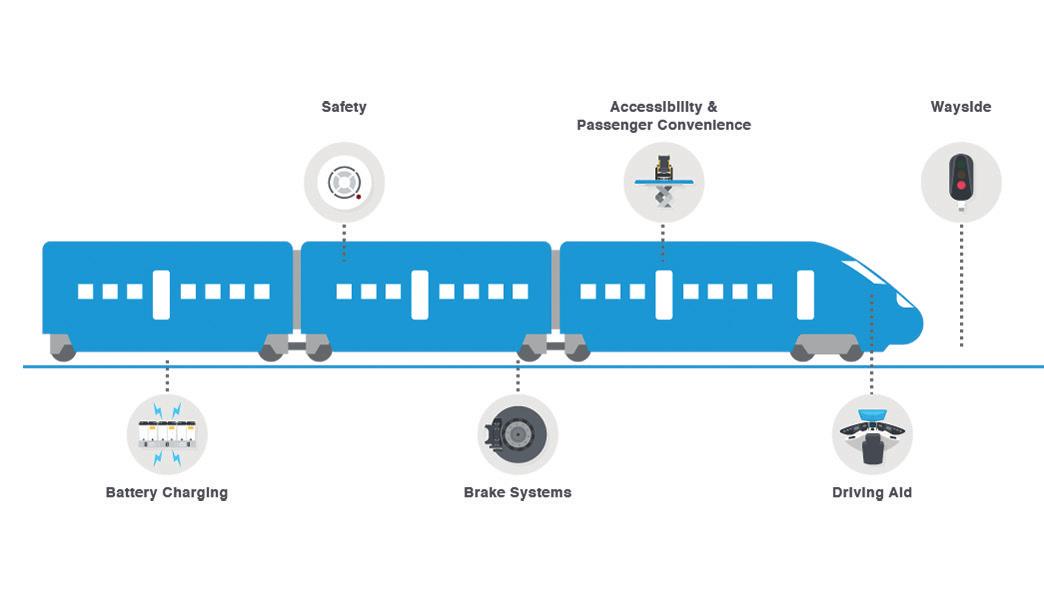

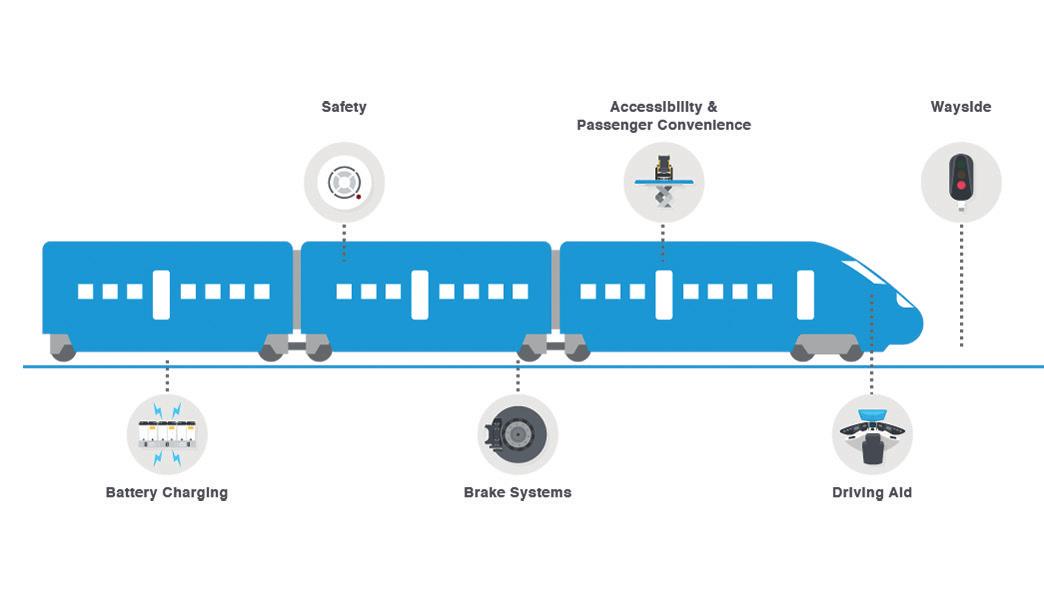

45 Selecting dc-dc converters for railway applications

The wide range of voltages and power levels required in modern trains puts a special focus on the role of the dc-dc converter.

CONTENTS POWER ELECTRONICS HANDBOOK • FEBRUARY 2023 CHECK US OUT on ISSUU.COM! CONNECT WITH US!

Circuit Protection

•Fuses & Fuse Accessories

•PTC Resettable Fuses

•TVS Diodes

•Varistors

•ESD Suppressors

Supercapacitors Magnetics

•Coin Cells

•Cylindrical Cells

•Large Cells

•Modules

•Systems

•Hybrid Cells

•Power Inductor

•High Current

•Transformers

•EMC (RF / EMI) Filters

•DC-DC Converters

Terminal Blocks Sensors

•Single Row / Barrier Strip

•Euromag / IEC Style

•Edge Connector

•Temperature Sense

•Current Sense

Eaton offers a range of electronics components that include power and EMC magnetics solutions, circuit protection, supercapacitors and terminal blocks products. These products serve customers in computing, consumer, energy, industrial, medical and transportation markets. Learn more on our website: Eaton.com/electronics Contact us: Eaton.com/ELXContactUs

DESIGN WORLD

FOLLOW THE WHOLE TEAM ON TWITTER @DESIGNWORLD

EDITORIAL

VP, Editorial Director Paul J. Heney pheney@wtwhmedia.com

@wtwh_paulheney

Senior Contributing Editor Leslie Langnau llangnau@wtwhmedia.com

@dw_3Dprinting

Senior Editor

Aimee Kalnoskas akalnoskas@wtwhmedia.com @eeworld_aimee Editor Martin Rowe mrowe@wtwhmedia.com @measurementblue

Associate Editor Emma Lutjen elutjen@wtwhmedia.com

Executive Editor Lisa Eitel leitel@wtwhmedia.com @dw_LisaEitel

Senior Editor Miles Budimir mbudimir@wtwhmedia.com

@dw_Motion

Senior Editor Mary Gannon mgannon@wtwhmedia.com

@dw_MaryGannon

Managing Editor Mike Santora msantora@wtwhmedia.com

@dw_MikeSantora

VP, Creative Services Mark Rook mrook@wtwhmedia.com

@wtwh_graphics

Senior Art Director Matthew Claney mclaney@wtwhmedia.com @wtwh_designer

Senior Graphic Designer Allison Washko awashko@wtwhmedia.com @wtwh_allison

Graphic Designer Mariel Evans mevans@wtwhmedia.com @wtwh_mariel

Director, Audience Development Bruce Sprague bsprague@wtwhmedia.com

IN-PERSON EVENTS

Events Manager Jen Osborne jkolasky@wtwhmedia.com @wtwh_Jen

Events Manager Brittany Belko bbelko@wtwhmedia.com

Event Marketing Specialist Olivia Zemanek ozemanek@wtwhmedia.com

Event Coordinator Alexis Ferenczy aferenczy@wtwhmedia.com

MARKETING

VP, Digital Marketing Virginia Goulding vgoulding@wtwhmedia.com @wtwh_virginia

Digital Marketing Coordinator

Francesca Barrett fbarrett@wtwhmedia.com @Francesca_WTWH

Digital Design Manager Samantha King sking@wtwhmedia.com

Marketing Graphic Designer Hannah Bragg hbragg@wtwhmedia.com

Webinar Manager Matt Boblett mboblett@wtwhmedia.com

Webinar Coordinator Halle Kirsh hkirsh@wtwhmedia.com

Webinar Coordinator Kim Dorsey kdorsey@wtwhmedia.com

FINANCE

CREATIVE SERVICES & PRINT PRODUCTION Controller Brian Korsberg bkorsberg@wtwhmedia.com

Accounts Receivable Specialist Jamila Milton jmilton@wtwhmedia.com

ONLINE DEVELOPMENT & PRODUCTION

Web Development Manager B. David Miyares dmiyares@wtwhmedia.com @wtwh_WebDave

Senior Digital Media Manager Patrick Curran pcurran@wtwhmedia.com @wtwhseopatrick

Front End Developer Melissa Annand mannand@wtwhmedia.com

Software Engineer David Bozentka dbozentka@wtwhmedia.com

Digital Production Manager Reggie Hall rhall@wtwhmedia.com

Digital Production Specialist Nicole Lender nlender@wtwhmedia.com

Digital Production Specialist Elise Ondak eondak@wtwhmedia.com

Digital Production Specialist Nicole Johnson njohnson@wtwhmedia.com

VP, Strategic Initiatives Jay Hopper jhopper@wtwhmedia.com

VIDEOGRAPHY SERVICES

Videographer Garrett McCafferty gmccafferty@wtwhmedia.com

Videographer Kara Singleton ksingleton@wtwhmedia.com

PRODUCTION SERVICES

Customer Service Manager Stephanie Hulett shulett@wtwhmedia.com

Customer Service Representative Tracy Powers tpowers@wtwhmedia.com

Customer Service Representative JoAnn Martin jmartin@wtwhmedia.com

Customer Service Representative Renee Massey-Linston renee@wtwhmedia.com

Customer Service Representative Trinidy Longgood tlonggood@wtwhmedia.com

WTWH Media, LLC

1111 Superior Ave., Suite 2600

Cleveland, OH 44114

Ph: 888.543.2447

FAX: 888.543.2447

DESIGN WORLD does not pass judgment on subjects of controversy nor enter into dispute with or between any individuals or organizations. DESIGN WORLD is also an independent forum for the expression of opinions relevant to industry issues. Letters to the editor and by-lined articles express the views of the author and not necessarily of the publisher or the publication. Every effort is made to provide accurate information; however, publisher assumes no responsibility for accuracy of submitted advertising and editorial information. Non-commissioned articles and news releases cannot be acknowledged. Unsolicited materials cannot be returned nor will this organization assume responsibility for their care.

DESIGN WORLD does not endorse any products, programs or services of advertisers or editorial contributors. Copyright© 2023 by WTWH Media, LLC. No part of this publication may be reproduced in any form or by any means, electronic or mechanical, or by recording, or by any information storage or retrieval system, without written permission from the publisher.

SUBSCRIPTION RATES: Free and controlled circulation to qualified subscribers. Non-qualified persons may subscribe at the following rates: U.S. and possessions: 1 year: $125; 2 years: $200; 3 years: $275; Canadian and foreign, 1 year: $195; only US funds are accepted. Single copies $15 each. Subscriptions are prepaid, and check or money orders only.

SUBSCRIBER SERVICES: To order a subscription or change your address, please email: designworld@omeda.com, or visit our web site at www.designworldonline.com

POSTMASTER: Send address changes to: Design World, 1111 Superior Ave., Suite 2600, Cleveland, OH 44114

6 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

2011 - 2020 2014 Winner 2014 - 2016

2013- 2017

Ferrite Cores with Distributed Air Gaps

Increased power density and optimized efficiency

TDK’s new standards for ferrite cores with distributed air gaps, enables increased power density and a further degree of downsizing compared to other technologies. In addition, cores with distributed air gaps offer the possibility to optimize the design of transformers and chokes in terms of efficiency and thermal performance.

• ETD, PQ and E cores with distributed air gaps are available as standard catalog types for many core sizes and various Al values.

• Ferrite cores with distributed air gaps allow for the use of a larger winding areas by reducing the fringing flux losses, offer significantly increased power density and improve the winding window fill ratio.

Typical Applications include:

– Onboard chargers and DC-DC converters for xEV vehicles

– Charging stations for EV

– Solar inverters

– Uninterruptible power supplies (UPS)

– Industrial switch-mode power supplies

www.tdk.com

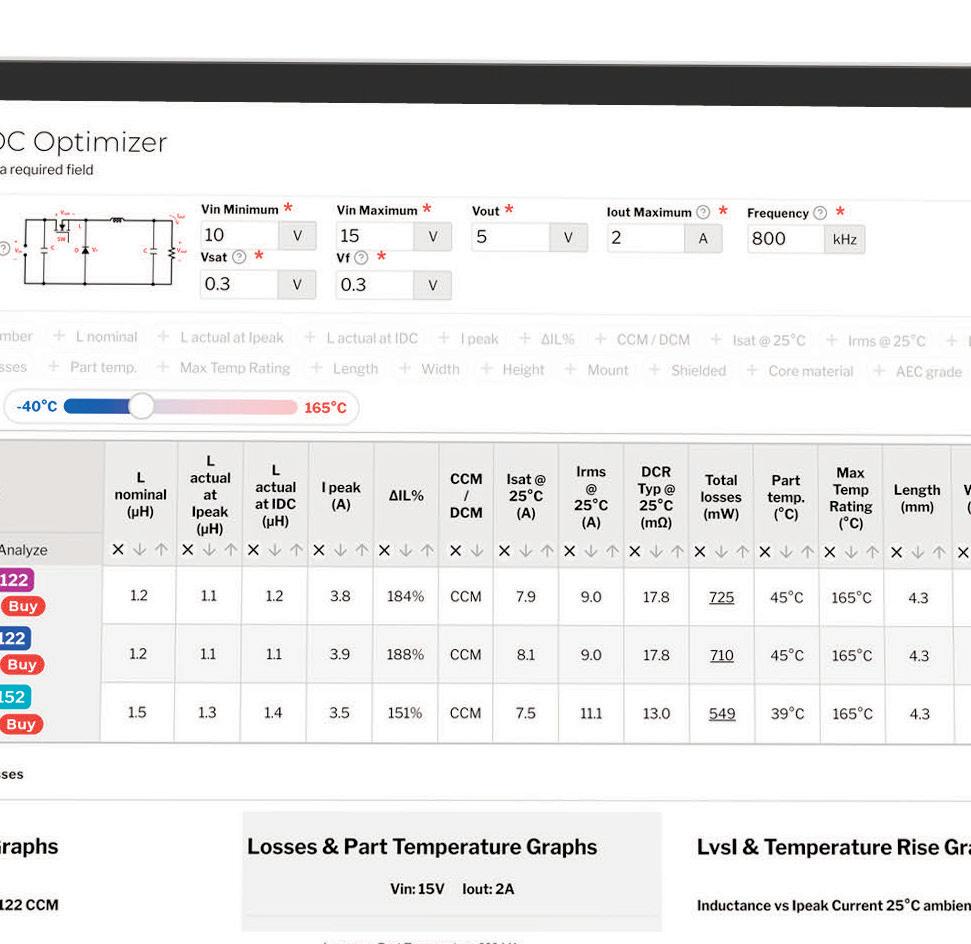

Extended Power Range GaN-based USB-C adapters and chargers deliver increased performance

Bredemeier, Principal Engineer for Power Systems and Solutions Division, Infineon Technologies

TheUniversal Serial Bus Power Delivery Specification (Revision 3.1, Version 1.1)

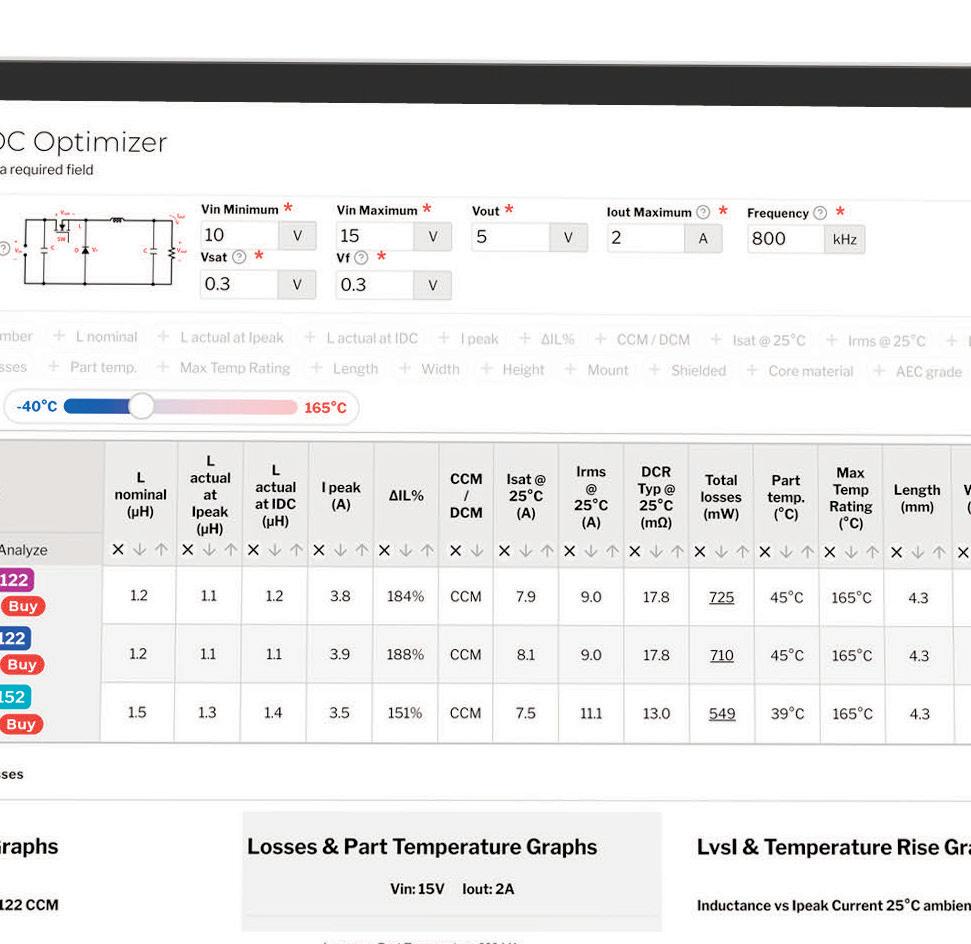

(USB-PD) standard enables higher power levels of up to 240 W. The wide output voltage range of 5 V to 48 V, however, raises new challenges for currently used converter topologies. The combination of an AC-DC power factor correction (PFC) boost and a DC-DC hybrid flyback (HFB) stage, also known as an asymmetrical half-bridge flyback topology, can provide the right solution for USB-PD chargers and adapters with wide input and output voltage ranges. Before discussing this approach, a little background on the latest USB standard is in order.

USB-PD Extended Power Range standard

The latest IEC 62680-1-2:2022 specification defines a power delivery system that addresses all elements of a USB system. This includes hosts, devices, hubs, chargers, and cable assemblies. The USB-PD Extended Power Range (EPR) standard with 28 V, 36 V, and 48 V fixed voltages offers a universal AC-DC adapter for many different purposes, charging a whole range of end devices, from smartphones to gaming laptops, up to power tools, and even e-bikes. It defines an adjustable voltage supply (AVS) mode that allows the device being powered to request intermediate voltages between 15 V and up to the maximum available fixed voltage in these systems. Electromagnetic compatibility, power factor correction, standby power, and average efficiency requirements raise challenges for the converter topologies

8 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com POWER ELECTRONICS HANDBOOK

Topology Size Efficiency Comments PFC+Flyback Requires bulky transformer Good Limited in switching frequency. PFC+LLC+Buck Small Very good Output voltage range limitations require a buck converter that negates the inherent size and efficiency. PFC+Hybrid Flyback Very small Very good Wide output voltage range. Transformer size can be reduced considerably from conventional flyback variants.

Peter

delivery.

Table 1. Comparison of key design characteristics for mid-power/ wide output voltage power

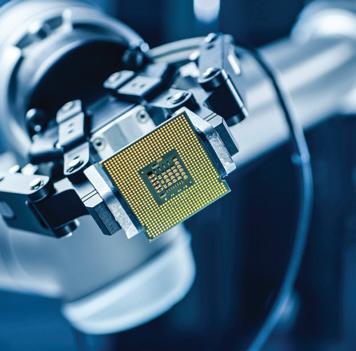

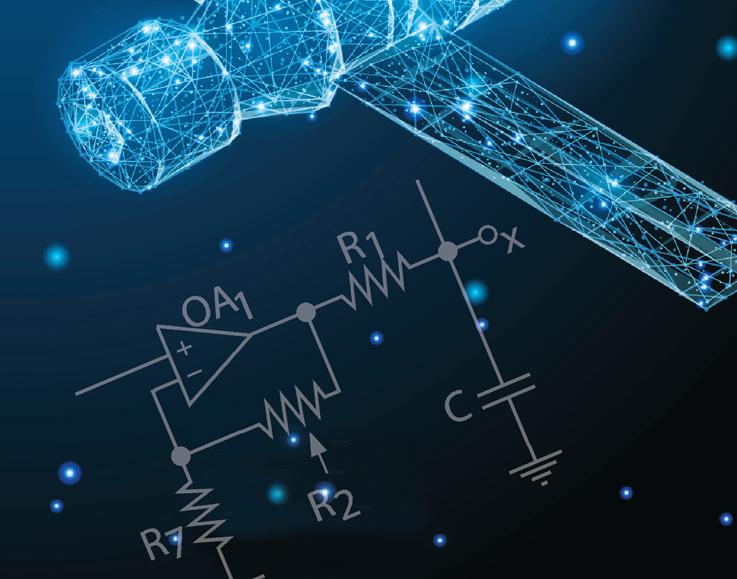

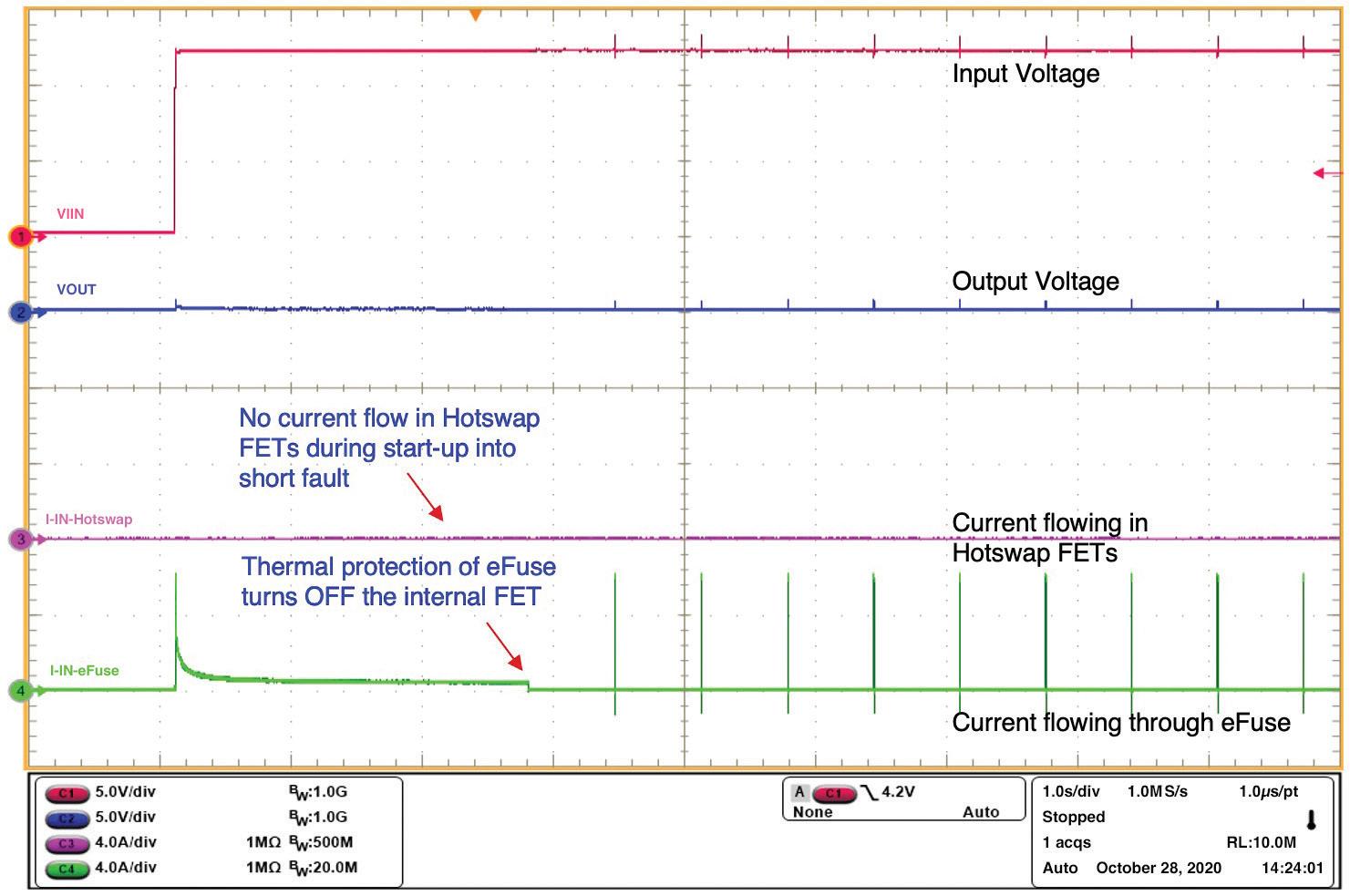

An innovative, highly integrated combo controller for the joint control of the PFC and the hybrid flyback stage.

used up to now. Additionally, the size and, consequently, the power density becomes a more critical factor for the end users.

Design options for state-of-the-art mid-power range with wide output voltage range circuit topologies include PFC+Flyback, PFC+LLC+Buck, and PFC+Hybrid flyback topologies. Table 1 summarizes the characteristics of these approaches.

With its small size and efficiency, the PFC+Hybrid flyback topology was chosen to meet the latest USB-PD EPR V3.1 standard. This architecture also enables a high-power density with high power efficiency design to meet other international regulatory standards, such as the European Union Code of Conduct (EU CoC) Version 5 Tier 2 requirements for external power supplies, and the U.S. Department of Energy (DoE) Level VI.

Since a wide variety of devices now rely on USB Type-C for connection, communication, and power, the USB Implementers Forum (USB-IF) uses independent test labs to certify conformance to the standard before manufacturers can identify and claim conformance on specific products.

Other certifications, such as IEC623681:2018, “Audio/video, information, and communication technology equipment – Part 1: Safety requirements,” need to be considered as well. In this case, non-compliant products cannot be sold in major markets after the effective date.

XDP™ Digital Power Controllers

Allowing system designers to easily implement a USB-PD EPR solution, a highly integrated XDP™ controller XDPS2221 controls both the PFC and the hybrid flyback stages. This integration offers optimal control of both stages to deliver maximum performance. To further simplify the system designer’s task, a 140 W ACDC reference design has been developed that achieves a full load peak efficiency of up to 95 percent and a high-power density of 22.67 W/ in3 (uncased) while delivering an output voltage from 5 VDC to 28 VDC, with input voltage range from 90 VAC to 264 VAC.

Proposed architecture

To achieve the highest power density, the proposed two-stage solution consists of an AC-DC PFC boost stage and the DC-DC hybrid flyback, combined with synchronous

rectification (SR) at the output. Figure 1 shows the details of the converter architecture. Gallium nitride (GaN) power devices were chosen for the switches of the PFC+HFB power stage. In addition to the three CoolGaN™ IGLD60R190D1 600V enhancement mode (e-mode) devices, the architecture uses OptiMOS™ FETs for the load switch and SR control, and the EZ-PD™ controller CCG3PA CYPD3175 for communication with the end device and output voltage management.

The XDPS2221 integrates an AC-DC power factor correction controller with a DC-DC hybrid flyback (HFB) controller, also known as an asymmetrical half-bridge (AHB), into a single 9.9 x 3.9-mm DSO-14 package. The integration includes a high-side driver coupled with a coreless transformer and a low-side driver driving the high- and low-side switches of the HFB stage, as well as a driver for the PFC switch. It enables a simple system structure out of the traditional flyback topology and provides the performance of a resonant half-bridge converter. Regulatory requirements can easily be met through the coordinated operation of the two stages.

Integrating all gate drivers, the GaN 600 V high voltage start-up cell for the initial IC voltage supply, and the certified active X-capacitor discharge for IEC62368-1:2018 conformance allow for a low external bill of material (BOM) and component count. Based on the zero-voltage switching (ZVS) HFB topology and GaN-based power devices, the design brings efficiency across various line/ load conditions. With these features and inherent topology advantages, such as ZVS and resonant energy transfer for transformer size reduction, system designs using the XDPS2221 can achieve very high-power densities.

The combo IC controller features a synchronous PFC and HFB burst-mode operation. The converter is switched on and off during light or no load to reduce the standby power for the lowest possible no-load input standby power performance. The quasi-resonant multimode PFC stage is enhanced with automatic PFC enable/disable functionality and adaptive PFC bus voltage control to maximize average and light load efficiency. Optionally, the integrated PFC function can also be disabled to support the use case with any external PFC controller.

The hybrid flyback stage uses peak current control operation for well-controlled regulation and fast dynamic load response. To ensure ZVS operation under all conditions, the hybrid

9 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com G a N-BASED USB-C

Figure 1. Proposed power architecture for a USB-PD EPR converter.

Figure 2. 140 W prototype USB-PD EPR 5 V – 28 V converter based on the XDPS2221 has a power density of 22.67 W/inch3

flyback features ZVS pulse insertion, including body diode cross-conduction prevention in the discontinuous conduction mode. Additionally, the XDPS2221 provides easy-to-configure parameters via a graphical user interface (GUI) to optimize system performance.

The embedded digital core of the integrated controller allows a sophisticated control algorithm to optimize the performance of both power stages. For optimum system efficiency and reduced standby power, the PFC stage will only be enabled depending on input and output voltage conditions and load conditions. In addition, a bus voltage target modulation, depending on the operation point of the HFB, helps to increase the efficiency even further.

To reach the highest power density, it is desired to maximize the efficiency at the maximum load, typically the worst case in terms of power losses. With the newly implemented PFC modulation, it is possible to improve the efficiency for the lower output voltage levels; the modulation can enhance efficiency by nearly five percent for the lowest output voltage.

The embedded digital core supports system fine-tuning by configurable parameters. This gives designers the flexibility to adapt to different power levels and application requirements. Additionally, very high-frequency switching applications can be supported and enable the usage of a planar transformer due to zero voltage switching and zero current switching (ZCS).

Practical prototype

To demonstrate the described advantages, a 140 W (28 V/5 A) prototype has been developed (Figure 2). In this case, two-layer PCBs and standard magnetic cores are utilized to achieve low system cost.

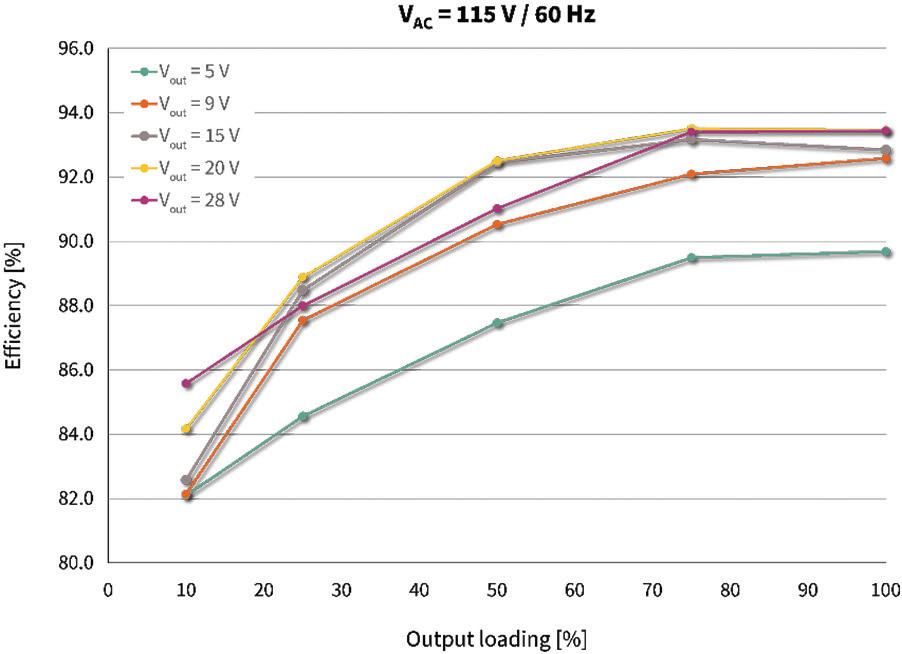

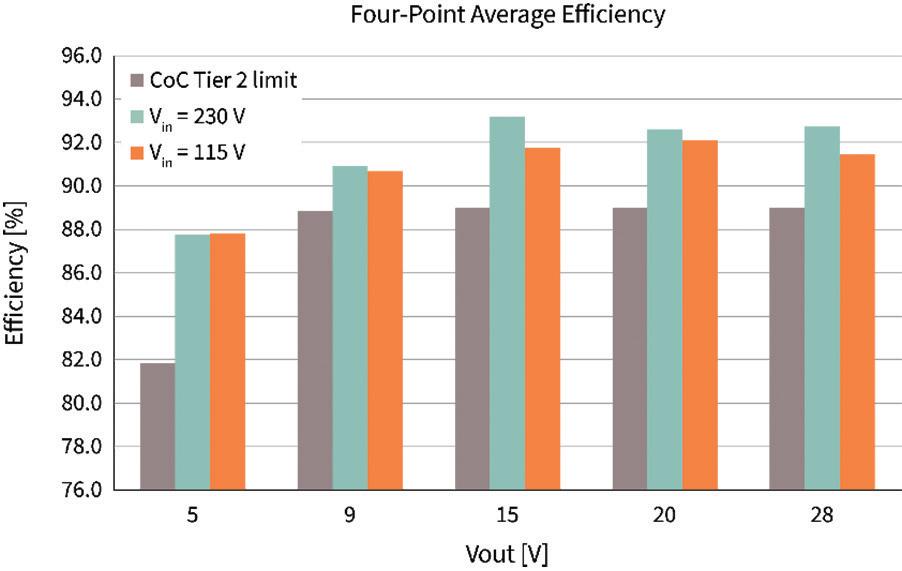

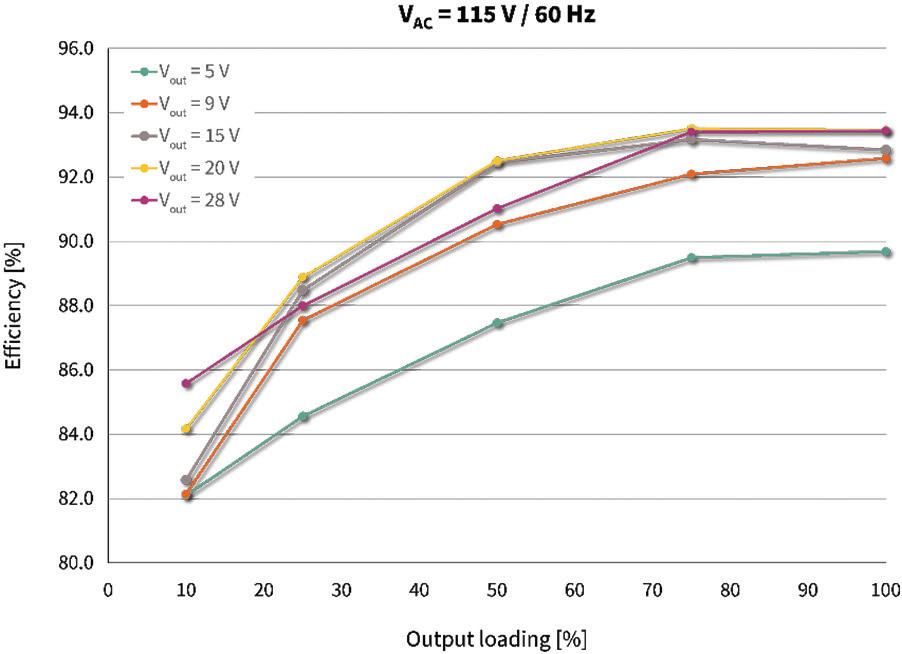

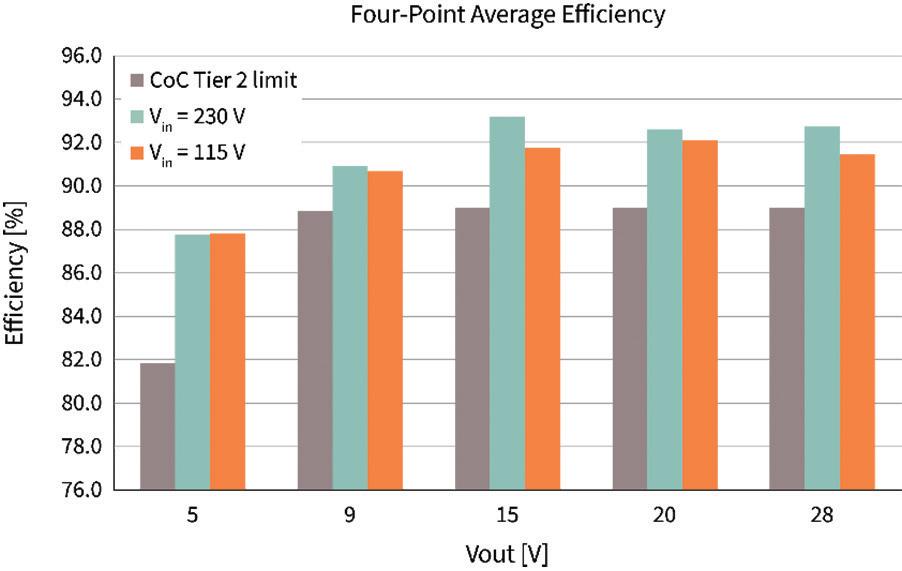

The efficiency results are shown in Figures 3 (low line) and 4 (high line). The results cover the output voltage range of 5 V – 28 V with load variation from 10 – 100%. The circuit reaches a peak efficiency of 95% at maximum load but stays above 80% efficiency at minimum load. This results in the following four-point average efficiency shown in Figure 5. With the integrated sophisticated control algorithm between PFC and HFB, the CoC Tier 2 limits can be easily achieved.

Due to the synchronous PFC and HFB burst mode operation, the standby losses in the input voltage that range from 90 VAC up to 264 VAC could be decreased below 70 mW over the entire input voltage range.

Meeting evolving standards

The USB-PD Extended Power Range standard defines requirements for power delivery in higher power ranges for a variety of applications that use the USB Type-C connector. Combining the HFB and the PFC-boost with the control strategy demonstrates the potential for USB-PD EPR adapters to reach high efficiencies from light load to maximum load. The highly integrated controller with combined PFC and HFB operation enables a simple design in a small size to achieve a high-power density. The benefits of the proposed solution have been demonstrated with a 140 W USB-PD EPR prototype achieving high peak efficiency of 95% and a power density of 22.67 W/in3 with a low-cost two-layer PCB.

10 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com POWER ELECTRONICS HANDBOOK

Figure 3. Low line efficiency vs. output loading for a voltage range of 5 – 28 VDC.

Figure 4. High line efficiency vs. output loading for a voltage range of 5 – 28 VDC.

Figure 5. Four-point average efficiency results indicate that the CoC Tier 2 limits can be easily achieved.

Capacitor Solutions for Aerospace, Defense, Energy & Communications

Hybrid wet tantalum capacitors—the most power dense in the industry; SWaP optimized for missioncritical applications.

Patented ceramic capacitors for the most demanding high-frequency microwave, millimeter-wave, and 5G applications.

Multi-layer Polymer (MLP) capacitors, including our recently released hi-rel MLP capacitors, which provide the industry’s highest ripple current rating per C*V.

Standard and engineered high-reliability multilayer ceramic chip capacitors (MLCCs) and leaded MLC devices.

Visit us at APEC booth #842

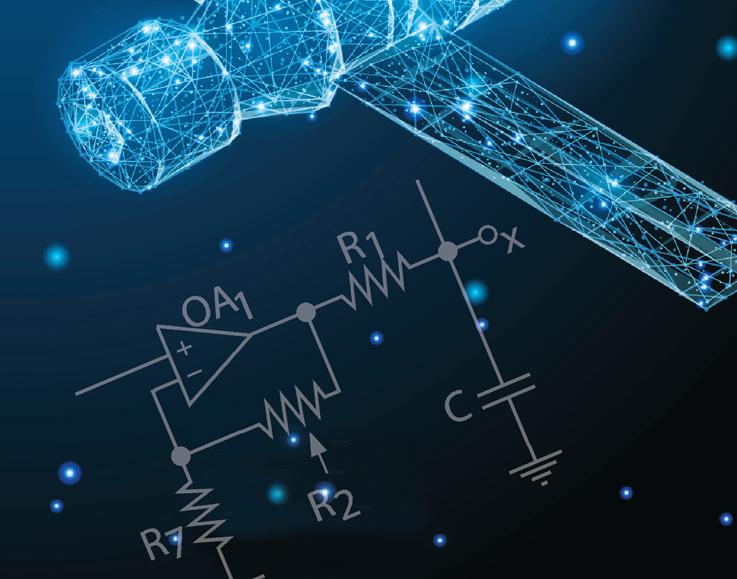

How to control dc microgrids

Microgrids are a great way to power locations where grid connections are unreliable, though it can be tricky to control them in robust ways.

Daniel Zammit, Dept. Industrial Electrical Power Conversion, University of Malta

Microgrids

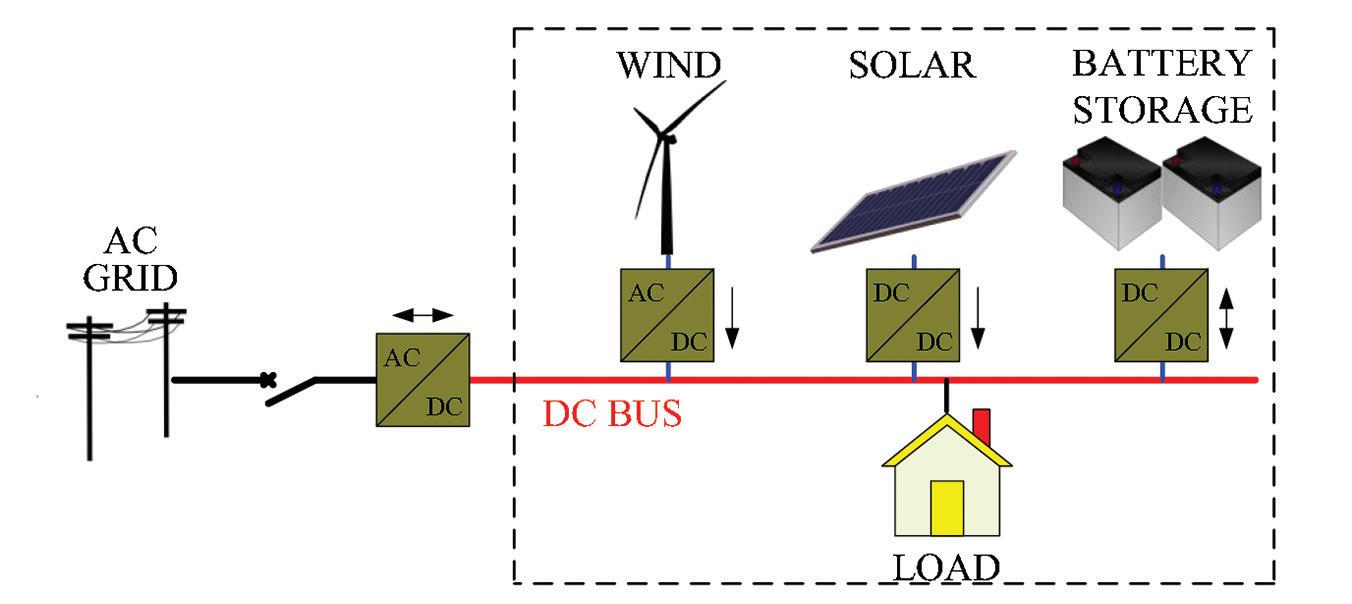

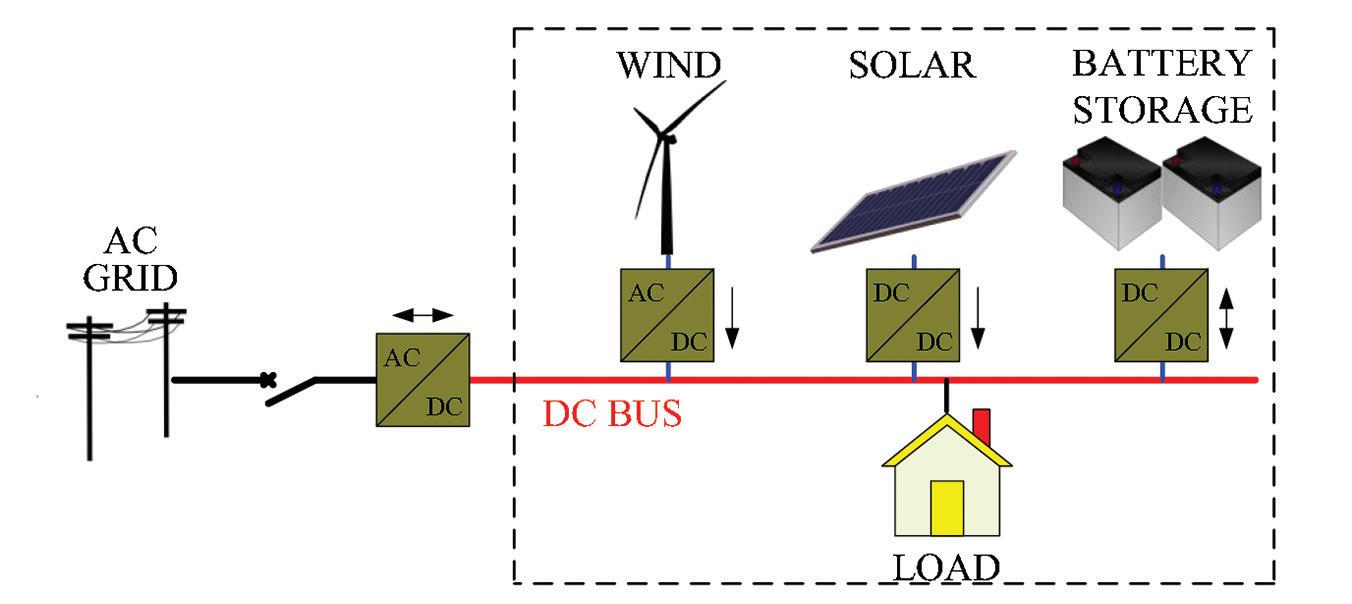

get a fair amount of press coverage these days thanks to their role in distributed power generation. A typical microgrid consists of distributed electrical power sources (e.g. photovoltaic systems, wind generation systems, etc.) and loads which together form a self sustainable electrical supply system, basically a small electrical grid.

The levels of control involved in a typical microgrid present challenges, giving rise to research opportunities aimed at perfecting the control systems that handle power converter integration in microgrid systems. Research in the field of dc microgrids spans topics ranging from control algorithms to improved load sharing among converters within the microgrid to algorithms that reduce operational costs,

all while simultaneoulsy trying to establish common standards with regard to control strategies, stabilization techniques, and standardization issues. Energy management within dc microgrids is also a popular research topic.

Microgrids can be ac, dc, or a combination of both. An attractive aspect of microgrids is the ability to connect with the grid as well as operate completely alone and autonomously in islanded mode. Of course, islanded mode operation is a great feature to have if the electrical grid fails. Different scenarios call for different ac or dc microgrid configurations. However, dc microgrids in particular are attracting a lot of research because they have lower conversion losses and fewer power conversion stages, no synchronization issues, and independence from power quality issues that arise on the ac grid.

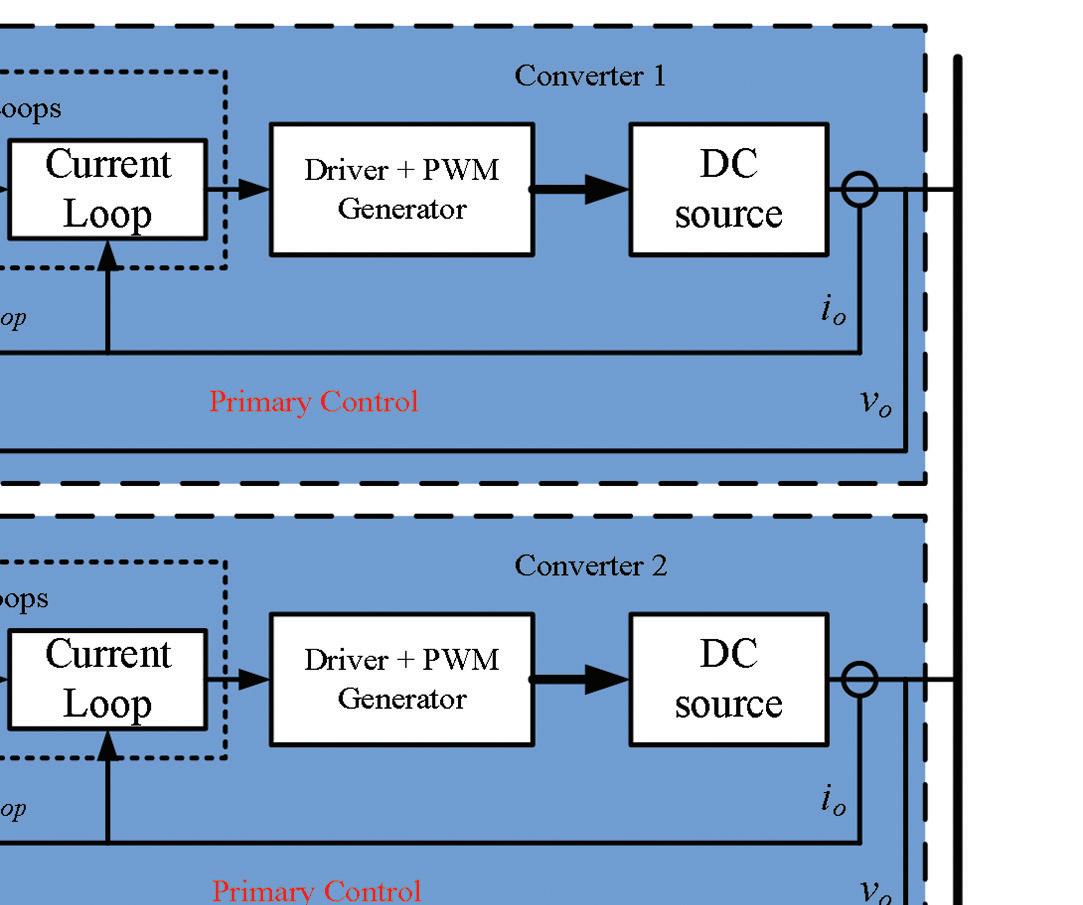

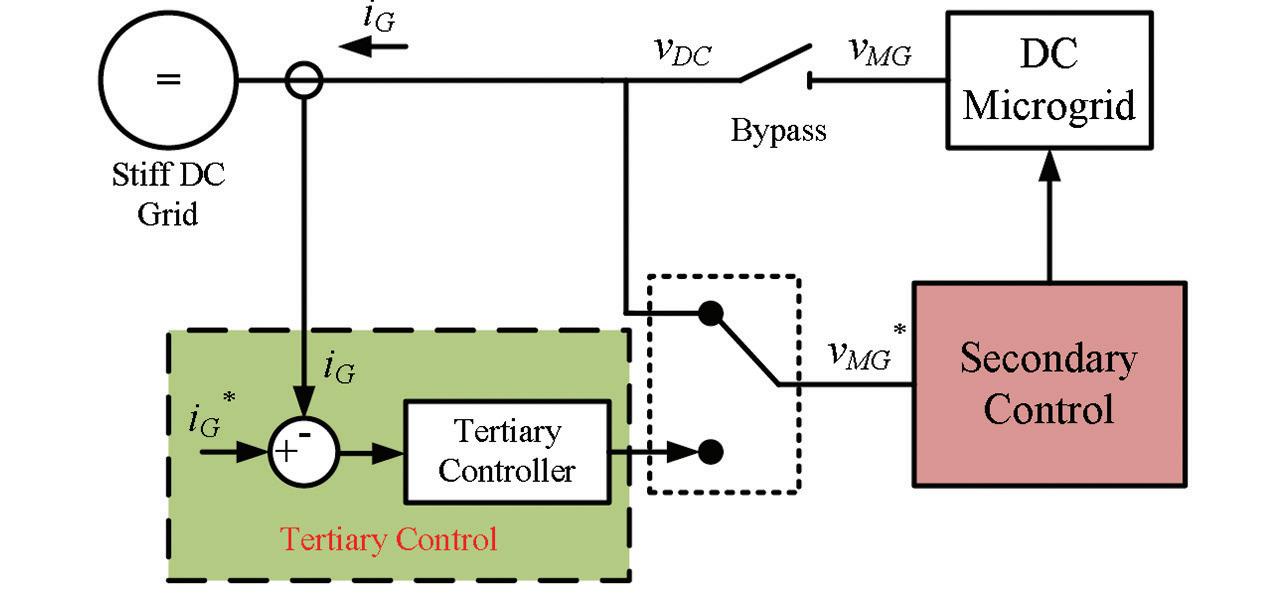

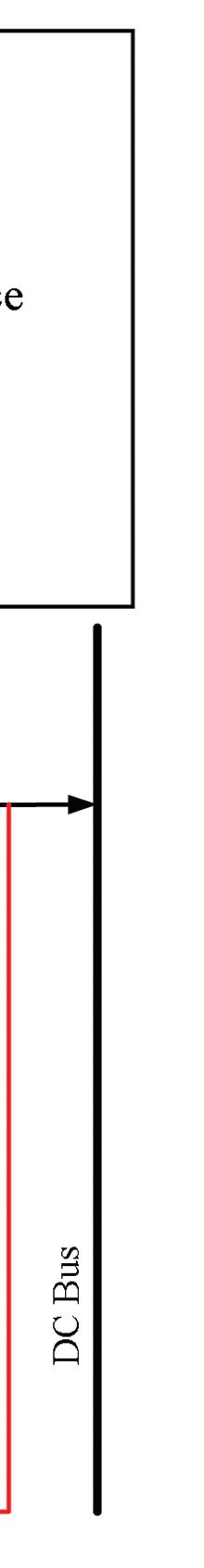

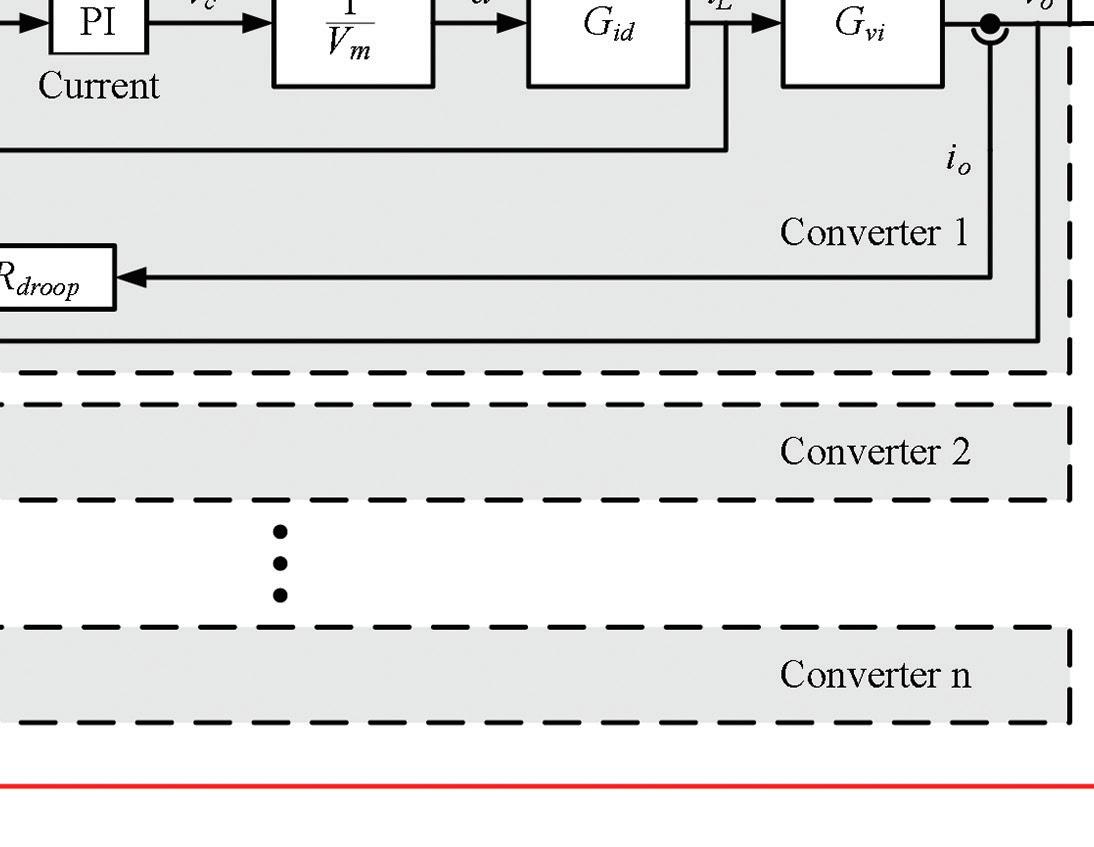

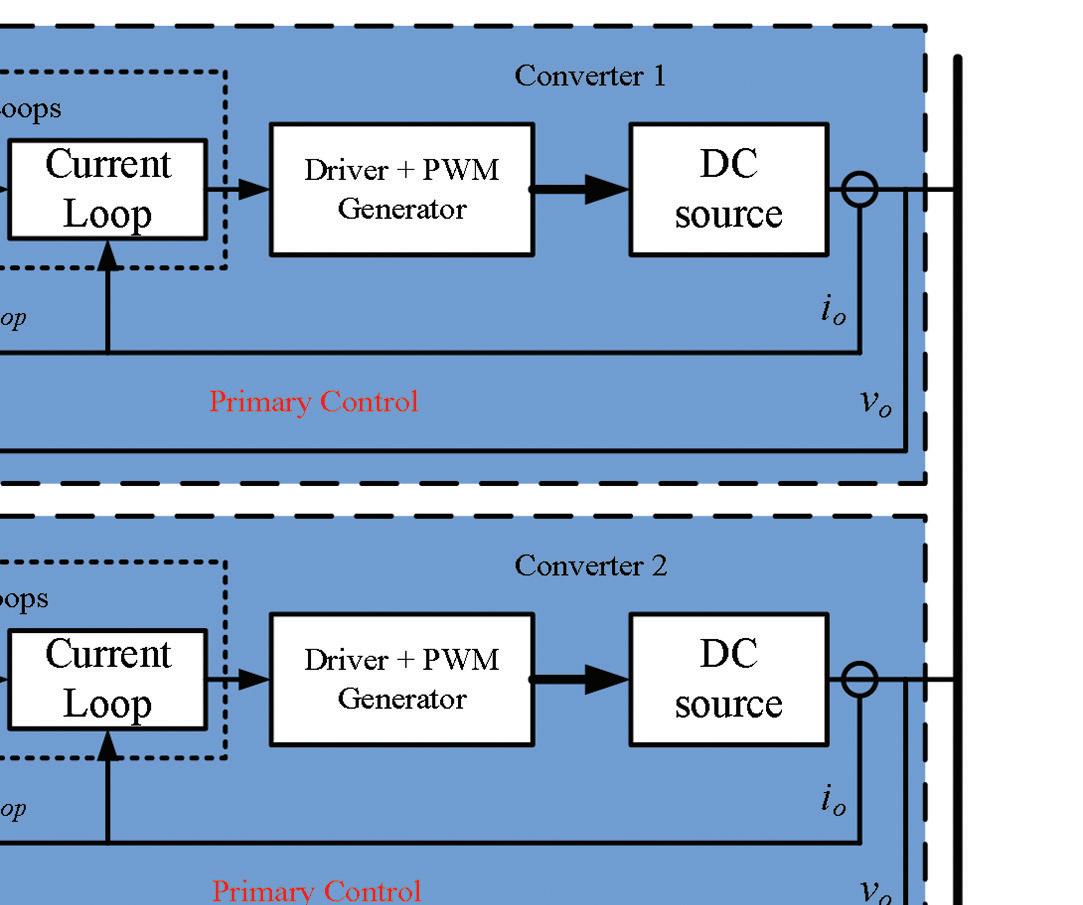

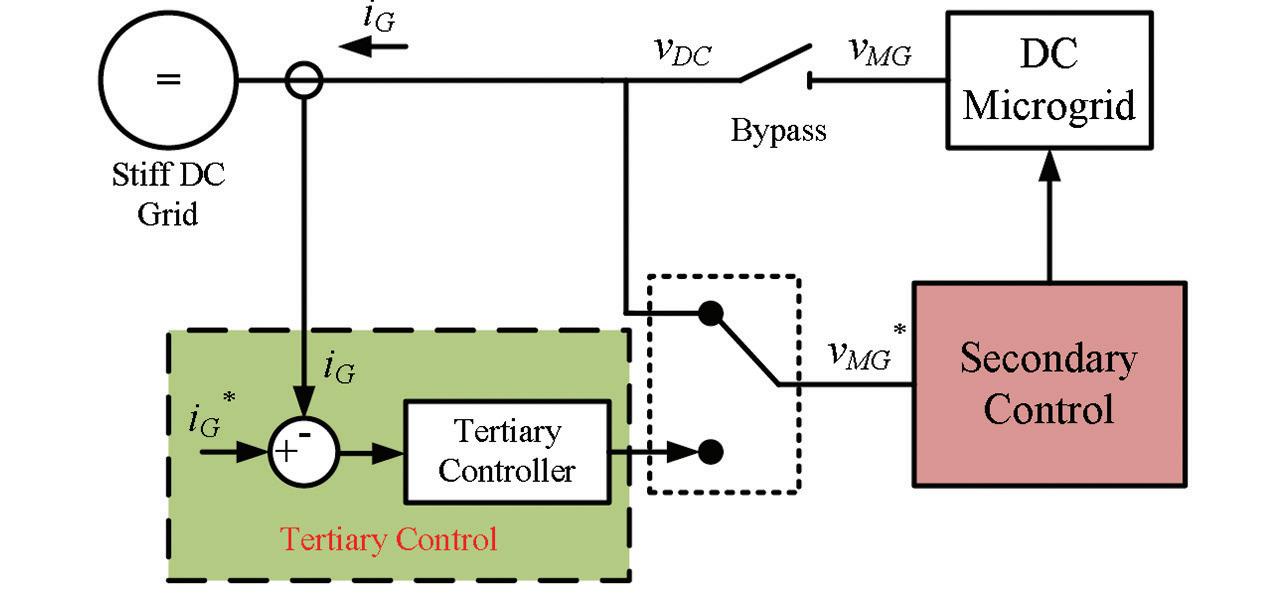

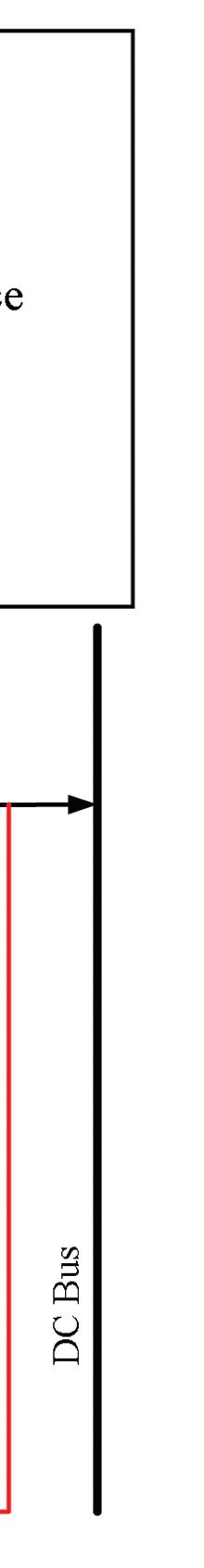

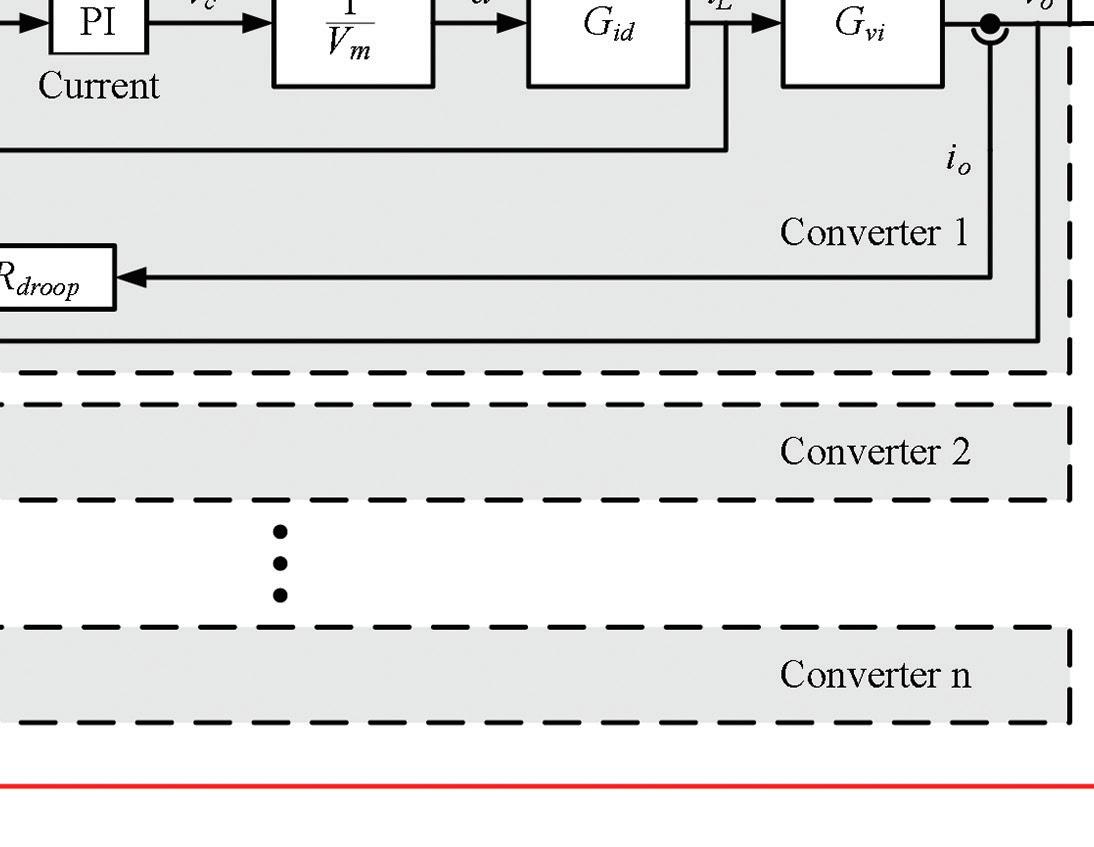

One of the main challenging aspects of microgrids is their internal controls. Different control systems within the microgrid system take care of the voltage, sharing of load current between the power converters, as well as charging and discharging of energy storage systems like batteries and supercapacitors. These control systems are generally organized in a hierarchical control system consisting of three levels: primary control local to each converter in the microgrid, including current and voltage control based on what’s called a droop control system; secondary control which restores deviations caused by the primary control, and tertiary control which handles the power flow between the microgrid and any outside electrical distribution system.

12 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

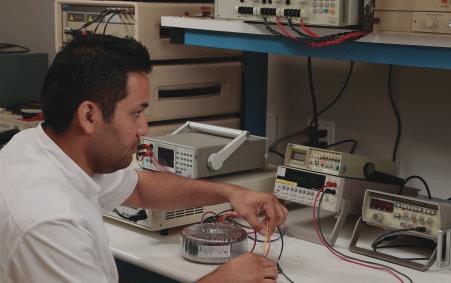

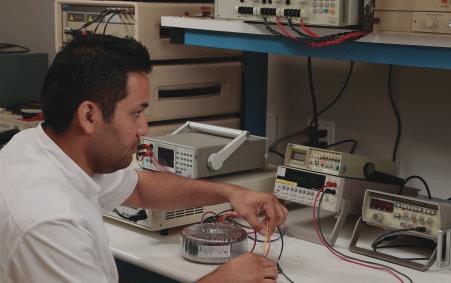

Experimental dc microgrid setups under investigation at the University of Malta. Research there has produced an innovative control system that shares current well within a dc microgrid.

POWER ELECTRONICS HANDBOOK

DC Microgrid Control System

Droop control is basically a way of equalizing current sharing among converters — it is analogous to reactive power sharing in an ac grid. Conventional droop control works by adding virtual resistance in various lines to equalize the currents. Droop control also prevents circulating currents between the power converters.

However, droop control creates voltage deviations in the microgrid, which creates a need for a voltage restoration controller within the secondary control. This voltage restoration controller is common to all power converters within the dc microgrid. It corrects the dc microgrid bus voltage to the desired value. In addition, another layer of control called tertiary control takes care of the flow of power inwards and outwards between the microgrid and the electrical grid.

Today, all these control algorithms are applied using microcontrollers, and the variables (like output current and output voltage) are sampled using ADCs. Generally, a microcontroller local to each power converter handles the primary control. Secondary control is taken care of by another microcontroller. It executes a secondary control algorithm which is common to all power converters within the dc microgrid.

A common microcontroller also generally takes care of tertiary control by monitoring and controlling the power flow or

Hierarchical Control System for dc Microgrids

current within, in, and out of the microgrid. Other higher-level control systems like Energy Management Systems (EMSs) are then employed to decide on any need to connect or disconnect to the main grid. These algorithms are generally based on the energy available in the microgrid.

Storage systems made up of battery banks integrated in the microgrid also have their higherlevel control algorithms like Battery Management Systems (BMSs) which decide when to charge and when to utilize the batteries. The power converter is controlled by the BMS, connecting the battery bank to the dc bus.

Primary control

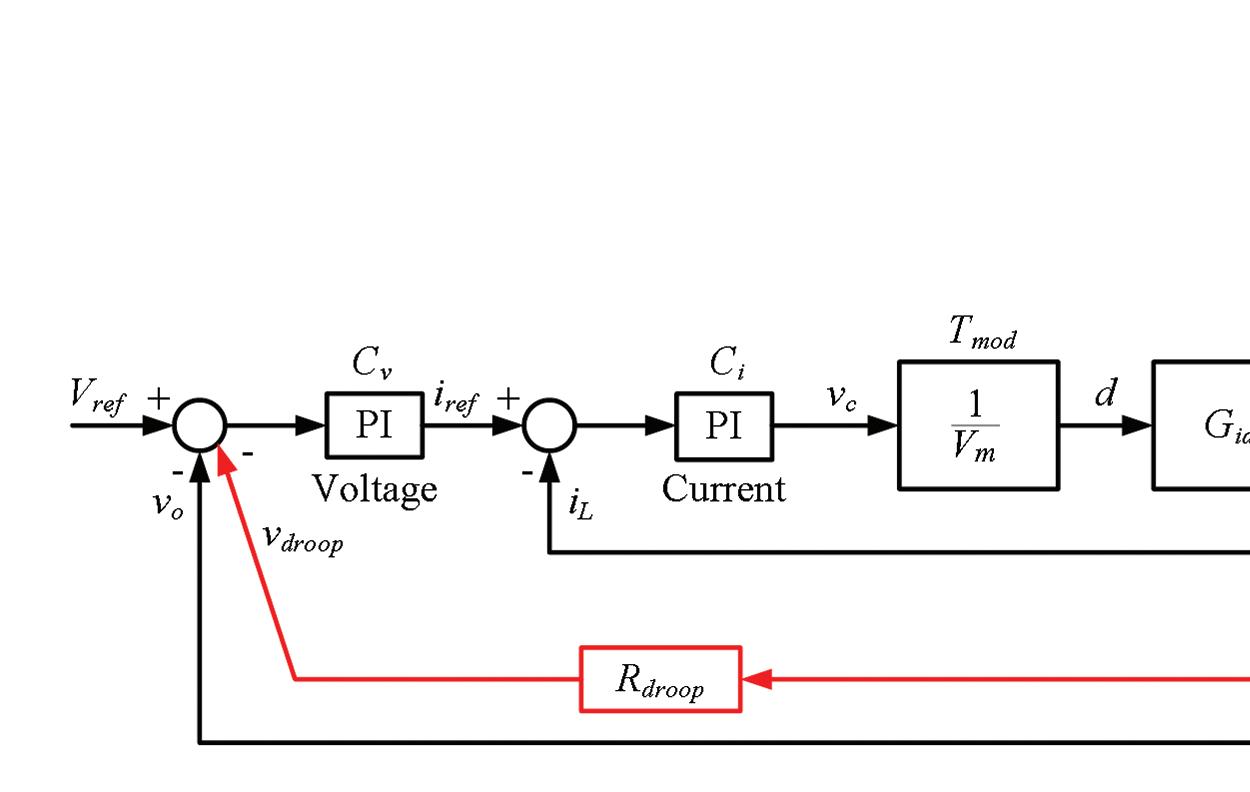

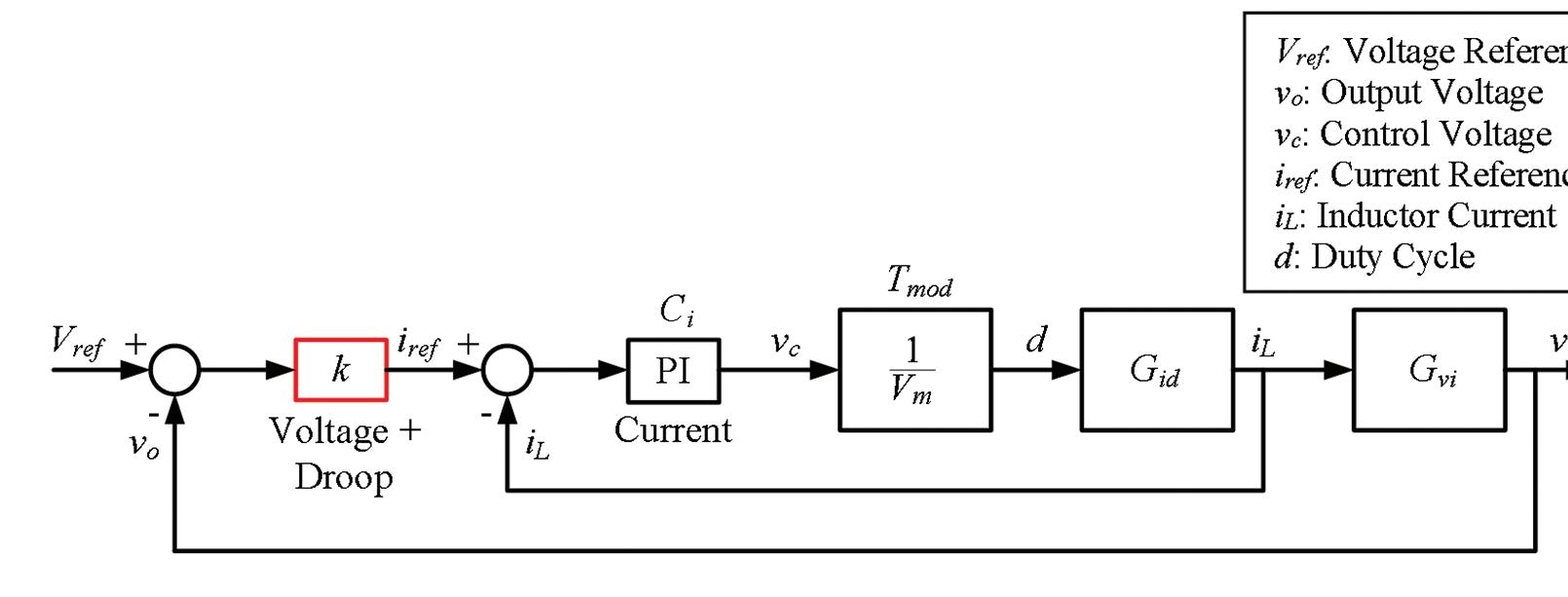

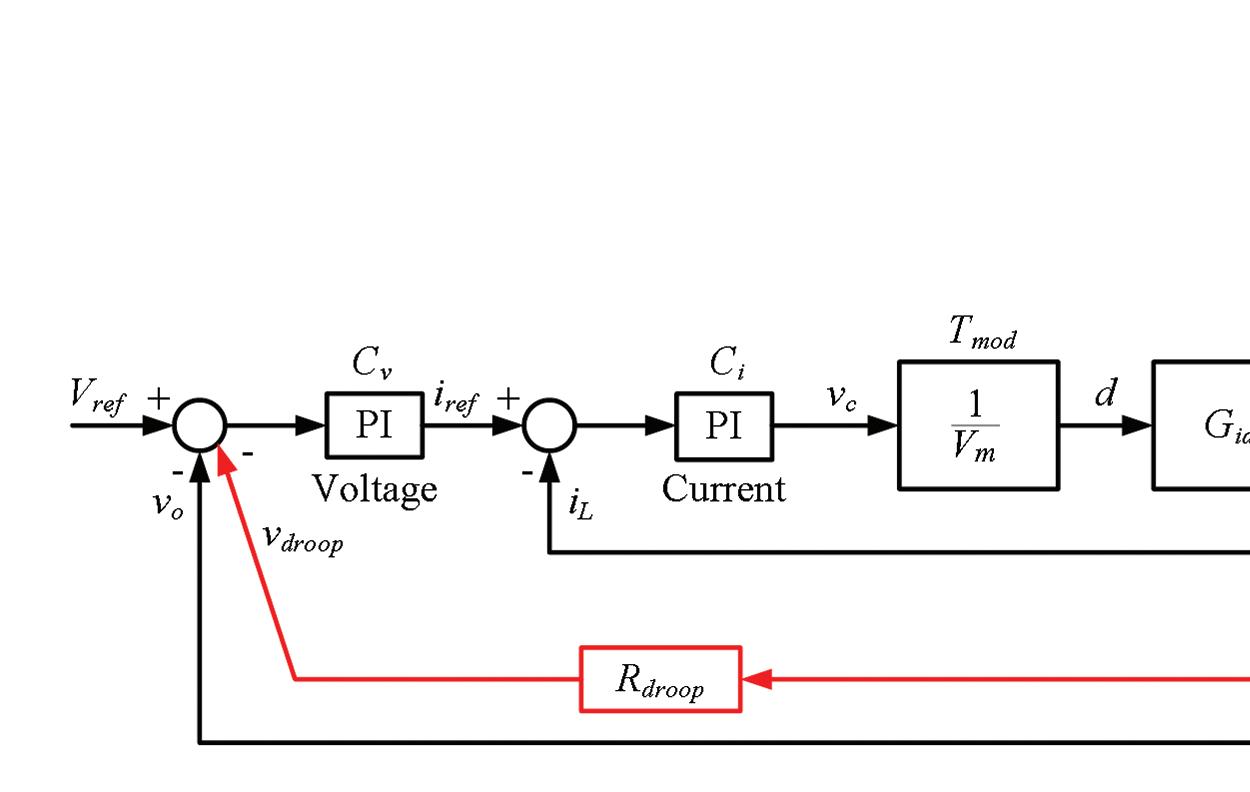

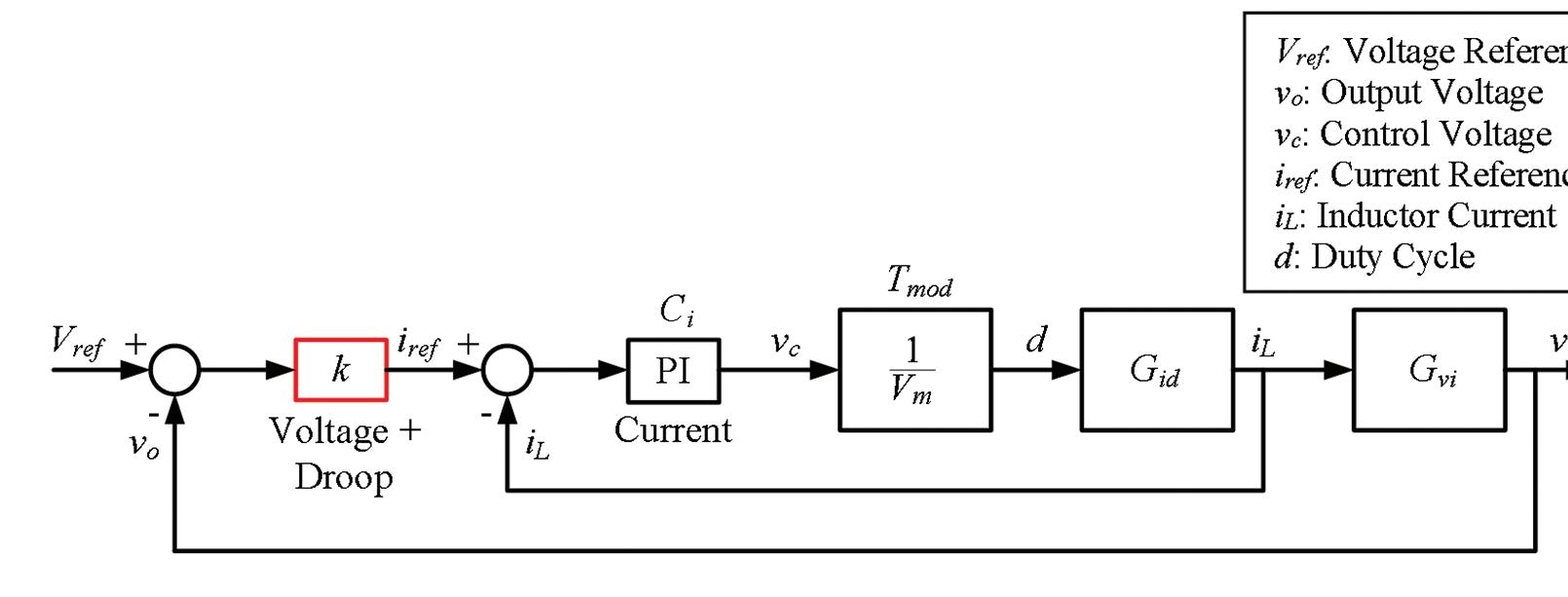

The main or primary control system for a dc/dc converter generally consists of nested current and voltage loops. When the converters are connected in parallel within a dc microgrid, droop control handles load sharing among the converters. The inner current loop controls the inductor current, while the outer voltage loop controls the converter output voltage. The inner current control

loop must be faster than the outer voltage control loop to minimize interaction between the two loops and prevent instability. Proportional Integral (PI) controllers control

the inductor current and output voltage. The current and voltage PI controllers, C (s) and Cv(s), are of the form C(s) = Kp +(KI/s), where KP is the proportional gain term and KI is the integral gain term.

The PI controllers are designed to produce the desired response and bandwidth of the control loop. These controllers make use of the transfer functions as shown in the nearby block diagram (Figure 3), where Tmod is the transfer function representing the pulse width modulation stage, Gid(s) is the transfer function of the relationship between the duty cycle and the inductor current, and Gvi(s) is the transfer function of the relationship between the inductor current and the output voltage. These transfer functions are based on the type of power converter in use (Buck, Boost, etc.).

13 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 2. (a) Primary and Secondary Control (b) Tertiary Control

CONTROLLING DC

Figure 3. Block Diagram of the Control System with Current and Voltage Control including V-I Droop

MICROGRIDS

In many of the dc microgrid operating modes, droop control handles load sharing between parallel-connected energy source converters by adjusting converter voltage and current control loop references. As mentioned before, this method prevents circulating currents among the parallelconnected converters, which would result if there were any differences in the converter output voltages.

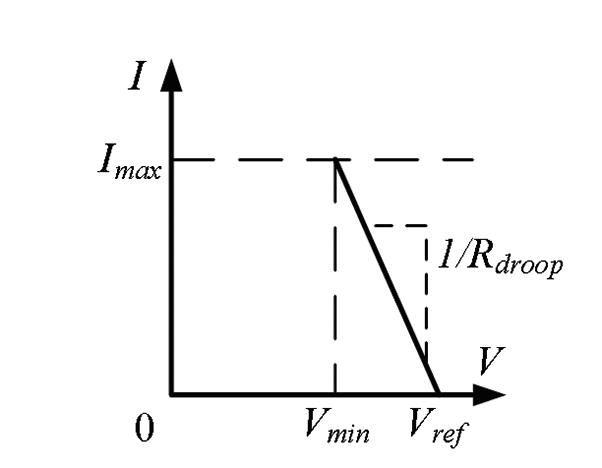

There are two main types of droop control methods: the impedance droop method (also referred to as V-I droop); and the admittance droop method, also referred to as I-V droop.

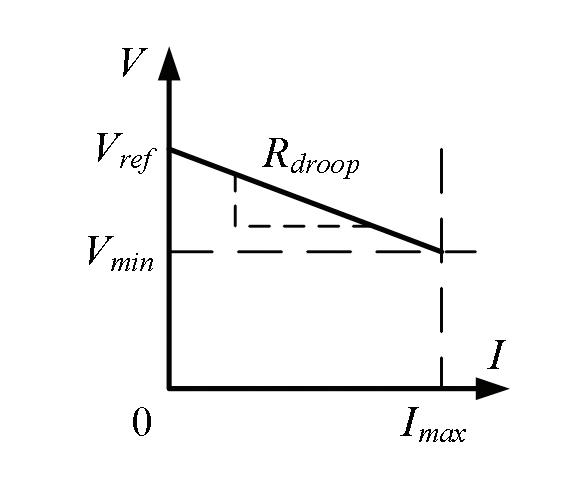

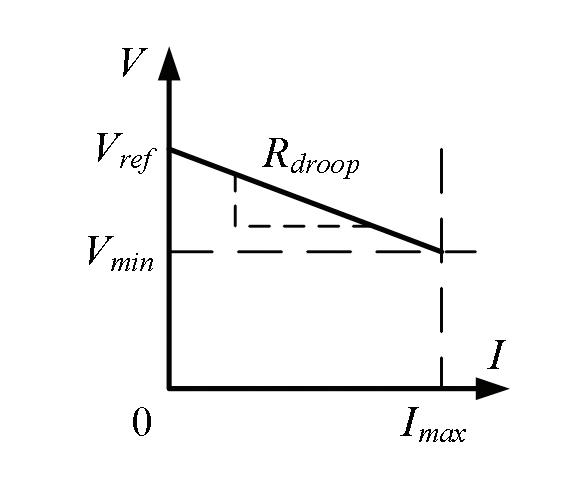

The V-I method can be considered the traditional droop control method. V-I droop is applied by inserting an additional loop containing a virtual resistance (Rdroop). The product of the output current and the droop virtual resistance is subtracted from the voltage reference. This causes a load-dependent deviation in the output voltage of the converter and thus a load sharing behavior between the parallel-connected

converters. The value of Rdroop is the slope of the V-I curve: Rdroop=(VrefVmin)/Imax = v /io_max where Vmin is the converter’s minimum permitted output voltage, Vref is the no-load output voltage reference, and Imax is the converter maximum current. io_max is the maximum output current and v is the maximum permissible voltage deviation calculated by v = Vref − Vmin

Therefore, the converter output voltage (vo) can be expressed as vo =Vref − Rdroopio, where io is the output current. In the case of a buck converter where the average inductor current and output current are about equal, the inductor current iL can be used instead of io in the control loop.

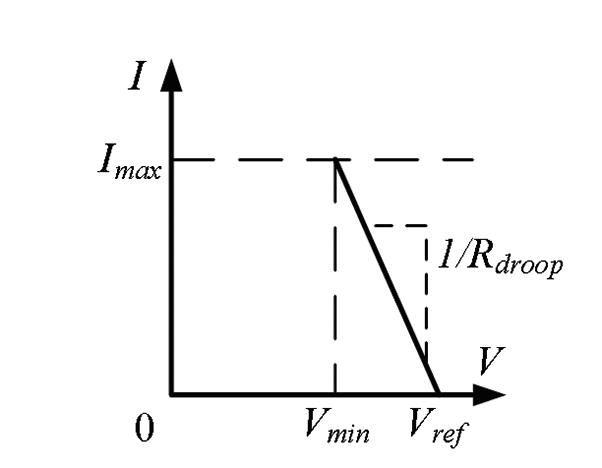

Now consider the I-V or Admittance Droop control method. Here the voltage PI controller is replaced with a multiplier term,

transfer function of the relationship between the inductor current and the output voltage.

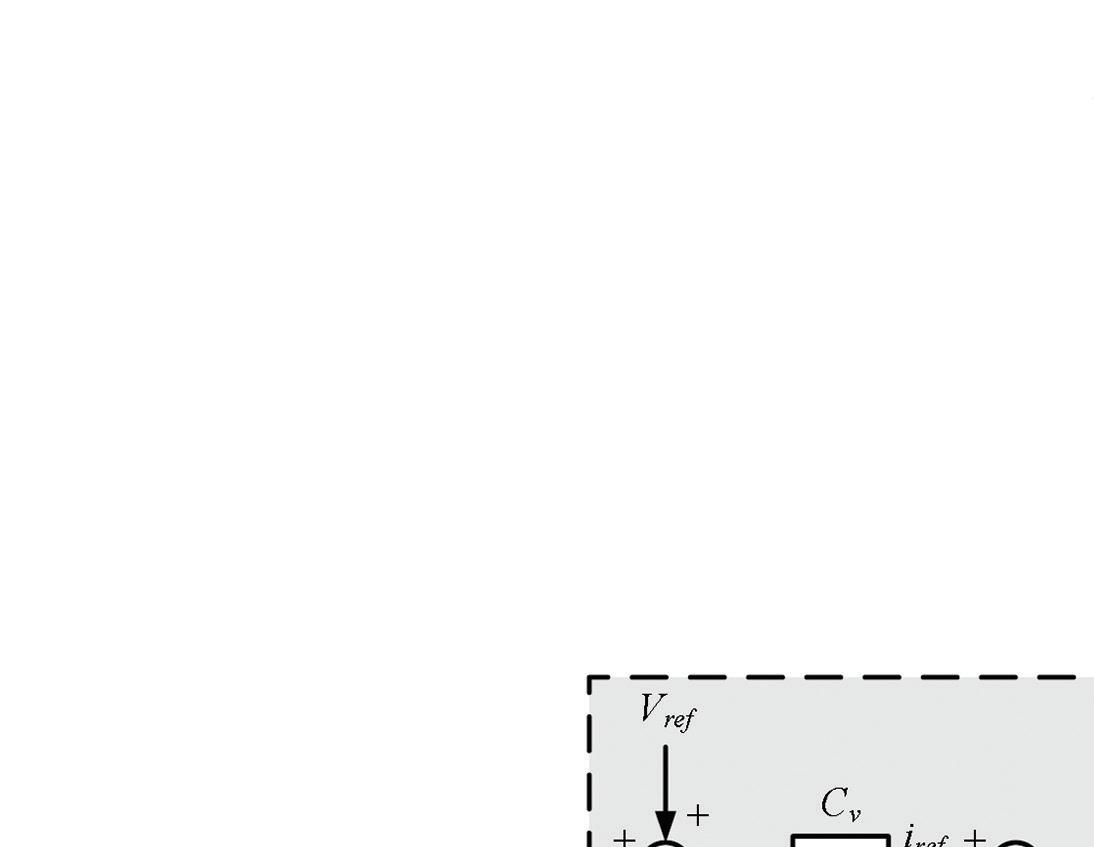

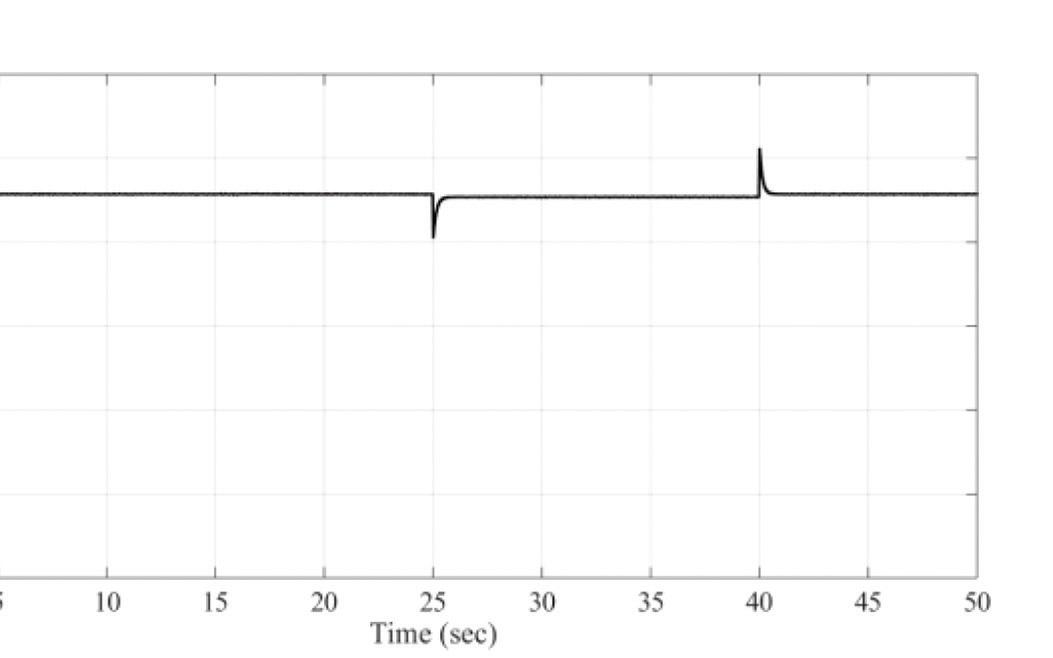

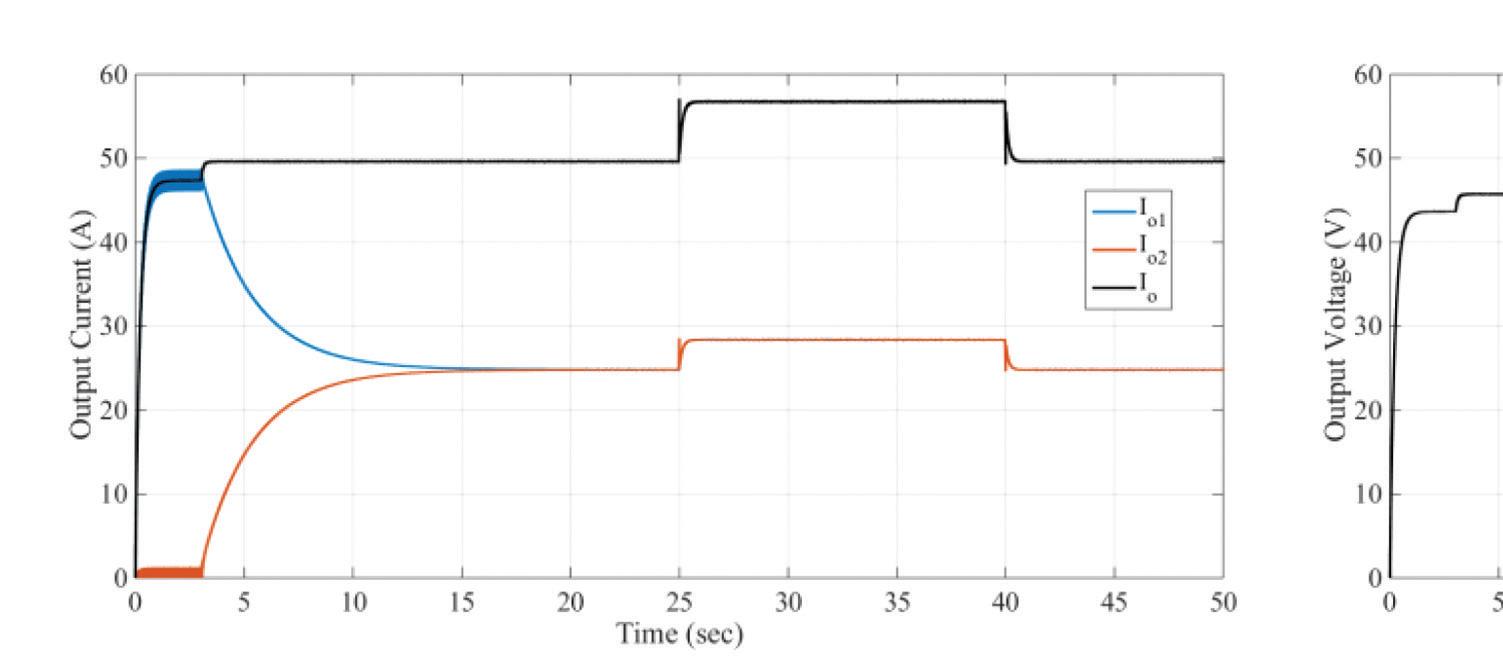

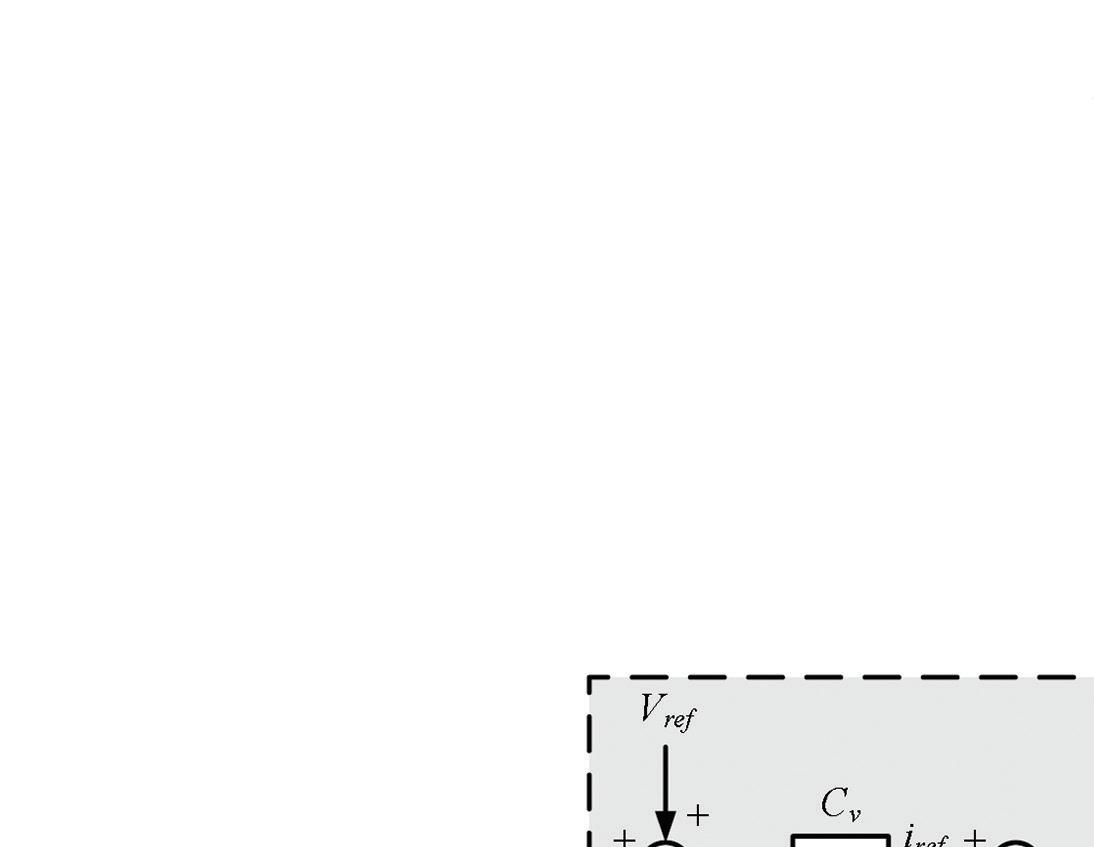

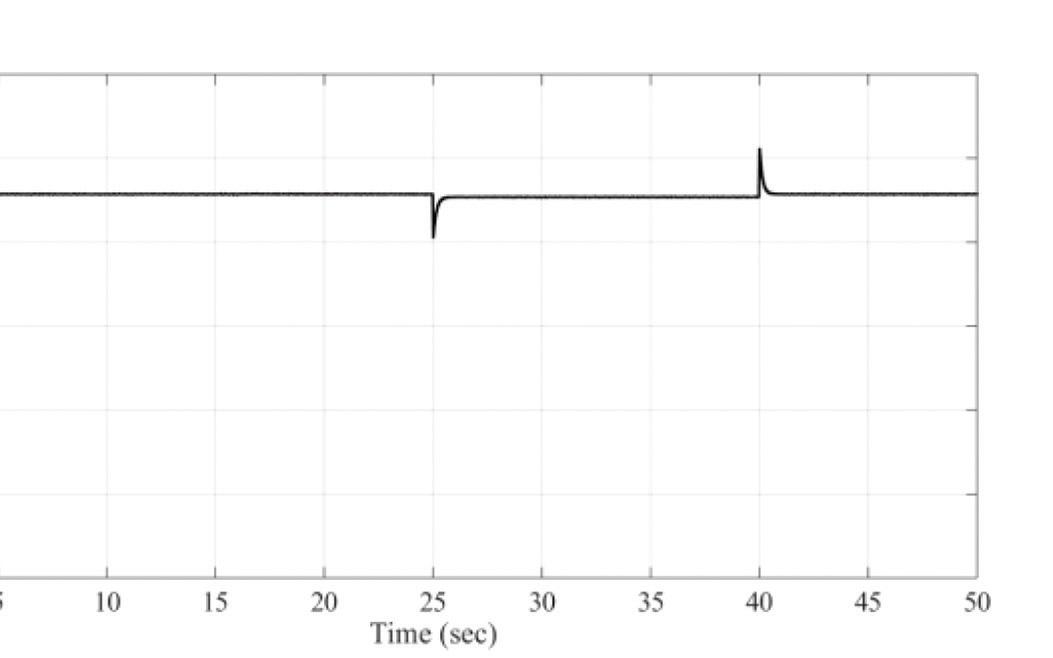

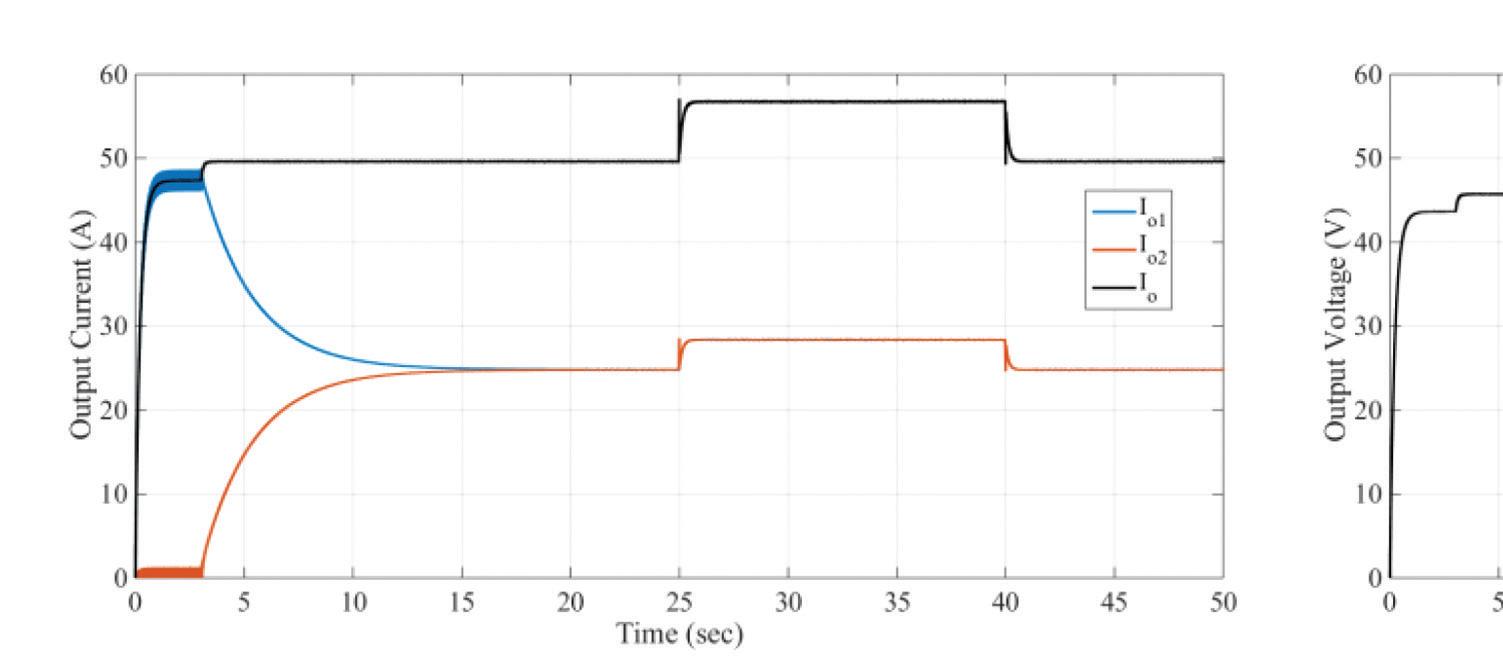

It is interesting to consider the simulation of two buck converters sharing a resistive load, Figures 6 and 7. The two converters were controlled by nested current and voltage PI controllers with a V-I droop loop. The droop resistance Rd was set to 0.092 Ω for both converters to share loads equally. The reference voltage for the voltage loop was 48 V.

Initially only one converter was switched on, supplying a resistive load of 0.92 Ω (52.08 A at 48 V for 2.5 kW). At t = 3 sec, the second converter was connected in parallel with the first and started sharing the resistive load. When the two converters operated in parallel, their respective droop loops adjusted each converter output

faster sharing, but at the expense of a bigger deviation in output voltage. Thus there’s a compromise between sharing speed and output voltage regulation.

Secondary control

As mentioned before, though droop control permits the sharing of a common load among paralleled converters, it also causes an output voltage deviation that depends on the load. The voltage deviation problem can be solved with a secondary controller. This controller forms an outer control loop common to all the converters/sources in the microgrid. This control loop compares the microgrid voltage with the desired voltage, and the PI compensator of the loop generates

thus this is strictly a proportionaltype controller. The multiplier is denoted by a constant value k, which effectively is the inverse of the droop virtual resistance Rdroop, k = 1/Rdroop. The multiplier term k is multiplied to the difference between the voltage reference and the actual output voltage to obtain the current reference for the current PI controller.

The plant transfer functions that are used to design the current PI controller and used with the multiplier term k are the same transfer functions as discussed earlier; Tmod is the transfer function representing the pulse width modulation stage. Gid(s) is the transfer function of the relationship between the duty cycle and the inductor current. Gvi(s) is the

voltage to share the load current. There was a change in load at t = 25 sec, decreasing the total resistive load to 0.8 Ω and causing a 15.2% change in load current. At t = 40 sec the resistive load changed back to 0.92 Ω.

Figure 7 shows the output current from each converter (Io1 and Io2) and the total output/load current (Io), during start-up, load sharing, and the load change, while Fig. 8 shows the output voltage (Vo) during the same process. It took about 13 seconds for load sharing between the two converters to reach steady state. The total output voltage rose from about 43.64 to 45.71 V, boosting the total output current from about 47.35 to 49.6 A. Increasing the droop resistance would make for

the voltage restoration needed for the primary control loops of each converter in the microgrid.

The demanded value of the voltage restoration loop (Vmgref in figure 9) is set to the desired dc microgrid voltage. The actual dc-bus microgrid voltage (vmg) is measured and fed back to this loop. This lets the controller generate the required restoration voltage (vres). The value of vres is restricted to prevent it from exceeding the maximum allowed voltage deviation.

With the V-I droop method, the equation for the output voltage (vo) is modified to include the restoration voltage: vo =Vref +vres − Rdroopio

Tertiary control manages power flow between a microgrid and external grid networks.

14 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 4. V-I DroopGraphical Representation

Figure 5. Graphical Representation of a I-V droop

POWER ELECTRONICS HANDBOOK

Figure 6. Block Diagram of the Control System with Current and Voltage Control including I-V Droop

This power flow management helps reduce power losses and optimizes power generation sources. Level of control can have various complexities that range from managing the connection of the microgrid to the grid, according to the load requirements and power availability within the microgrid, to complete management of the various power sources to maximize their output within the microgrid.

Research on dc microgrids

Many research groups in universities are interested in dc microgrid research. For example, the Dept. of Industrial Electrical Power Conversion at the University of Malta has researched microgrids, both ac and dc systems. There, an experimental laboratorybased 5-kW dc microgrid was set up for studies on energy control algorithms and converter prototypes. The experimental dc microgrid was designed and built in-house consisting of three power converters; two buck converters used to emulate energy sources and one bidirectional converter connecting a battery storage system.

Each converter prototype was designed to be open for further research development. Research has produced an innovative control system offering good performance in load current sharing within a dc microgrid. A battery management system was also designed to control energy flow in the battery storage unit. The plan is to keep developing the dc microgrid setup and the power converter prototypes, as well as the control system.

Companies and entities with interests in research collaborations and/or sponsorships are welcome, and can contact Dr Daniel Zammit using email daniel.zammit@um.edu.mt.

The research work in the area of dc microgrid at the Faculty of Engineering was carried out as a project by engineer Daniel Zammit as part of his doctorate studies, under the guidance of Prof. Cyril Spiteri Staines, Prof. Maurice Apap, and Dr. Alexander Micallef.

References

J. M. Guerrero, J. C. Vasquez, J. Matas, L. G. de Vicuna, and M. Castilla, “Hierarchical Control of Droop-Controlled AC and DC Microgrids – A General Approach Toward Standardization,” IEEE Transactions on Industrial Electronics, vol. Vol. 58, January 2011.

T. Dragicevic, X. Lu, J. C. Vasquez, and J. M. Guerrero, “DC Microgrids – Part I: A Review of Control Strategies and Stabilization Techniques”, IEEE Transactions on Power Electronics, Vol. 31, Issue 7, pp. 4876 – 4891, July 2016.

T. Dragicevic, X. Lu, J. C. Vasquez, and J. M. Guerrero, “DC Microgrids – Part II: A Review of Power Architectures, Applications and Standardization Issues”, IEEE Transactions on Power Electronics, Vol. 31, Issue 5, pp. 3528 - 3549, May 2016.

F. Gao, Y. Gu, S. Bozhko, G. Asher, and Pat Wheeler, “Analysis of Droop Control Methods in DC Microgrids”, IEEE 2014 16th European Conference on Power Electronics and Applications (EPE’14-ECCE Europe), 26-28 August 2014, Lappeenranta, Finland.

Y. Han, X. Ning, P. Yang, and L. Xu, “Review of Power Sharing, Voltage Restoration and Stabilization Techniques in Hierarchical Controlled DC Microgrids”, IEEE Access, Vol. 7, pp. 149202 –149223, 11 October 2019.

K. M. Bhargavi, N. S. Jayalakshmi, D. N. Gaonkar, A. Shrivastava, and

V. K. Jadoun, “A Comprehensive Review on Control Techniques for Power Management of Isolated DC Microgrid System Operation”, IEEE Access, Vol. 9, pp. 32196 – 32228, 19 February 2021.

S. Ali, Z. Zheng, M. Aillerie, J. P. Sawicki, M. C. Péra, and D. Hissel, “A Review of DC Microgrid Energy Management Systems Dedicated to Residential Applications”, Energies, Vol. 14, Issue 14, 17 July 2021.

D. Zammit, C. S. Staines, M. Apap, A. Micallef, ‘Alternative Droop Control Method using a Modified Lag Compensator for Paralleled Converters in DC Microgrids’, IEEE 6th International Conference on Control, Decision and Information Technologies (CoDIT’19), Paris, France, 23-26 April 2019.

D. Zammit, C. S. Staines, M. Apap, A. Micallef, ‘Paralleling Converters in DC Microgrids with Modified Lag I-V Droop Control and Voltage Restoration’, ELECTRIMACS 2019, Salerno, Italy, 21-23 May 2019.

D. Zammit, C. S. Staines, M. Apap, A. Micallef, ‘Paralleling Converters in DC Microgrids with Modified Lag I-V Droop Control and Voltage Restoration’, Chapter in book ELECTRIMACS 2019Selected Papers - Volume 2, Springer, 2020.

D. Zammit, M. Apap, A. Micallef, C. S. Staines, ‘A Battery Management System Applied to a Bidirectional Converter for a DC Microgrid Application’, publication in process.

15 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 7: Output Currents – V-I Droop – Two Buck Converters – Load Changes 0.92Ω - 0.8Ω

Figure 8: Output Voltage – V-I Droop – Two Buck Converters – Load Changes 0.92 Ω – 0.8 Ω

Figure 9. Block Diagram of the Voltage Restoration Control Loop

CONTROLLING DC MICROGRIDS

Simplifying designs for high power density applications

High-density power module technology for FPGAs, SoCs, & ASICs makes designing easy by providing the highest power densities in the smallest spaces.

Tony Ochoa, director of marketing,

Tony Ochoa, director of marketing,

Semiconductor integration has been proceeding at its typical breakneck pace, still following Moore’s Law. Each generation of ICs introduces new power demands with less space to satisfy them. As clever as some have been, powering solutions have always traded off power density against size and ease of use; a power module that does not force engineers to play any of these qualities against any other can go a long way to eliminating those trade-offs.

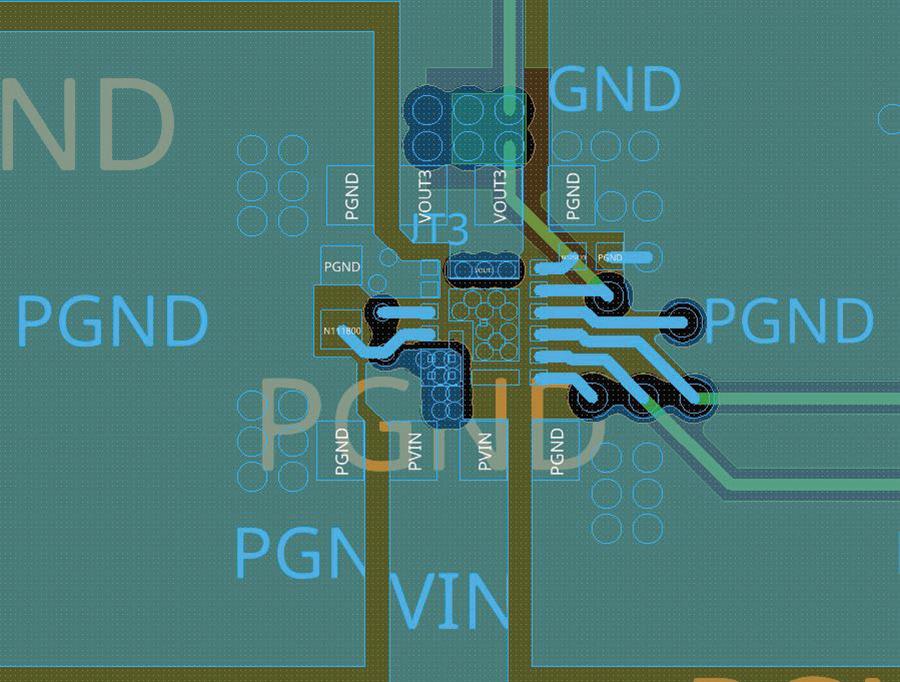

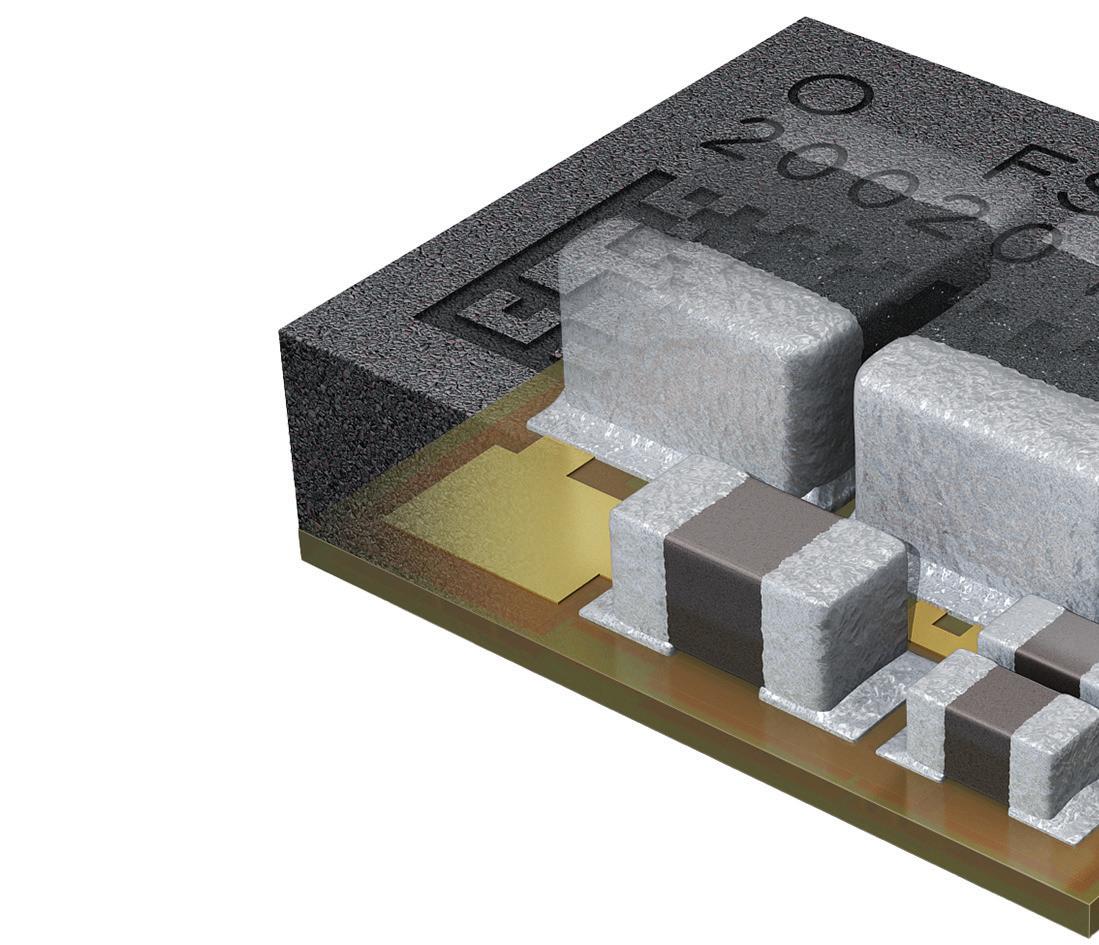

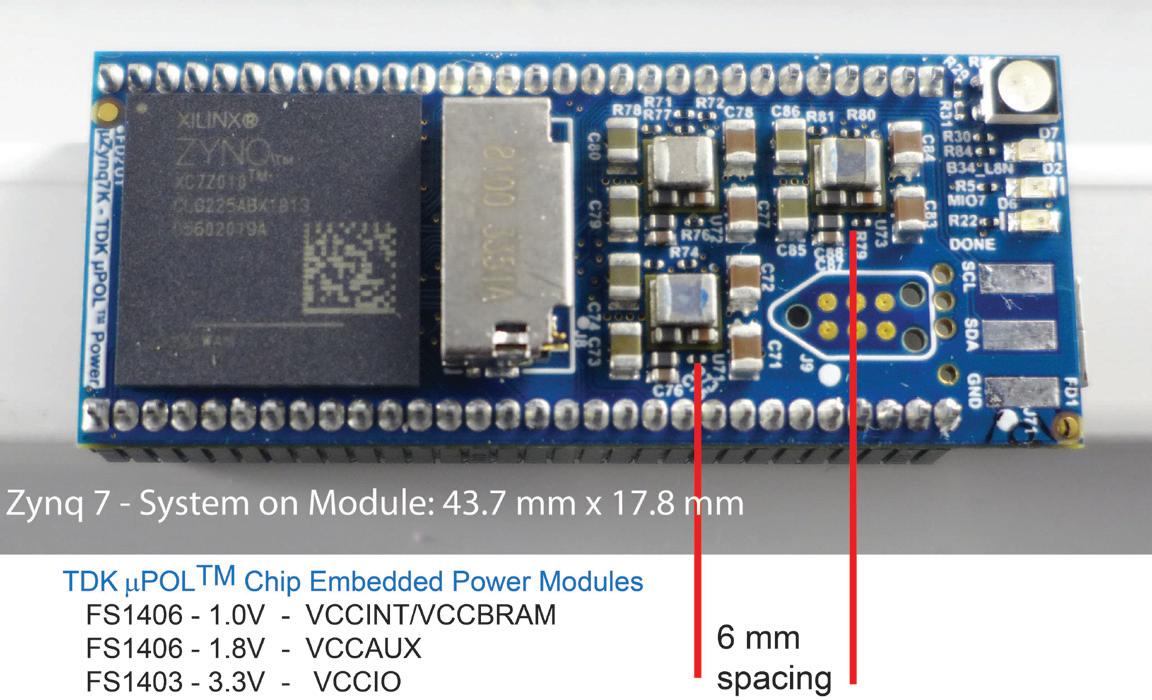

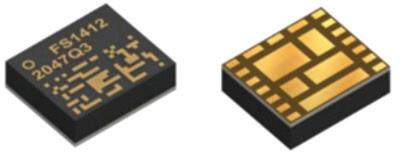

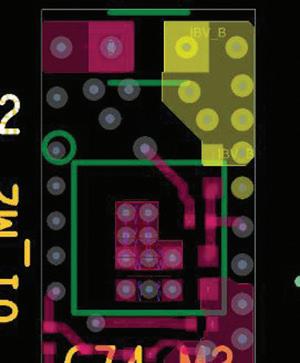

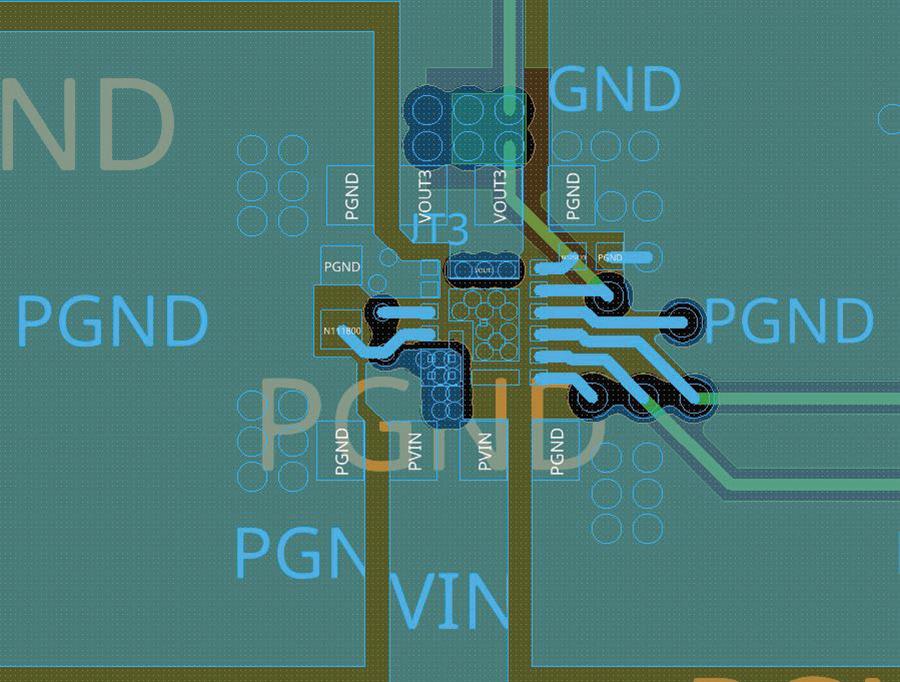

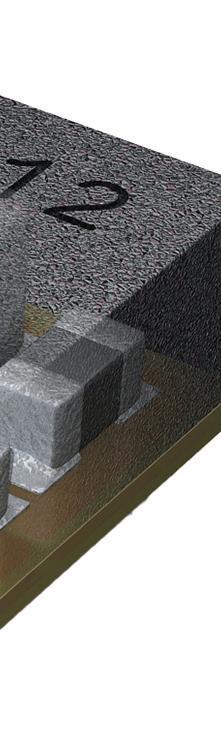

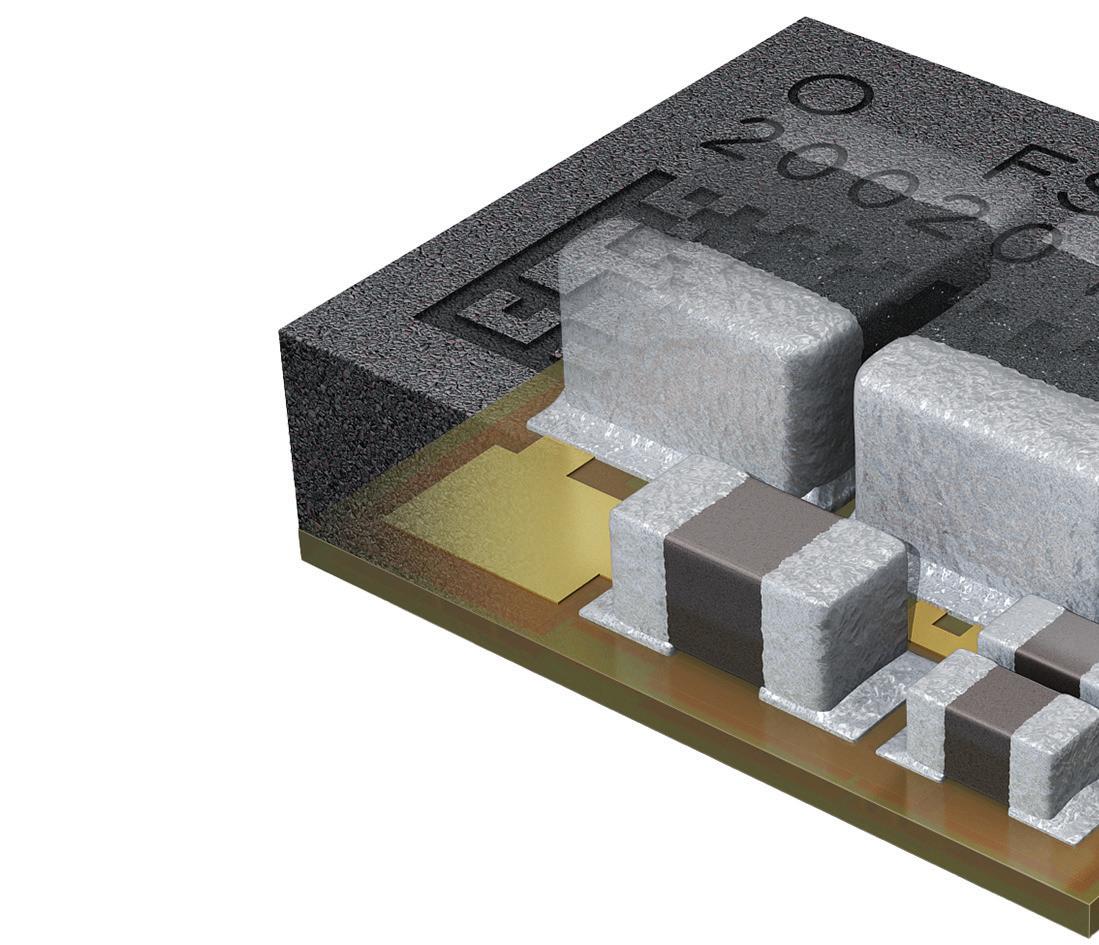

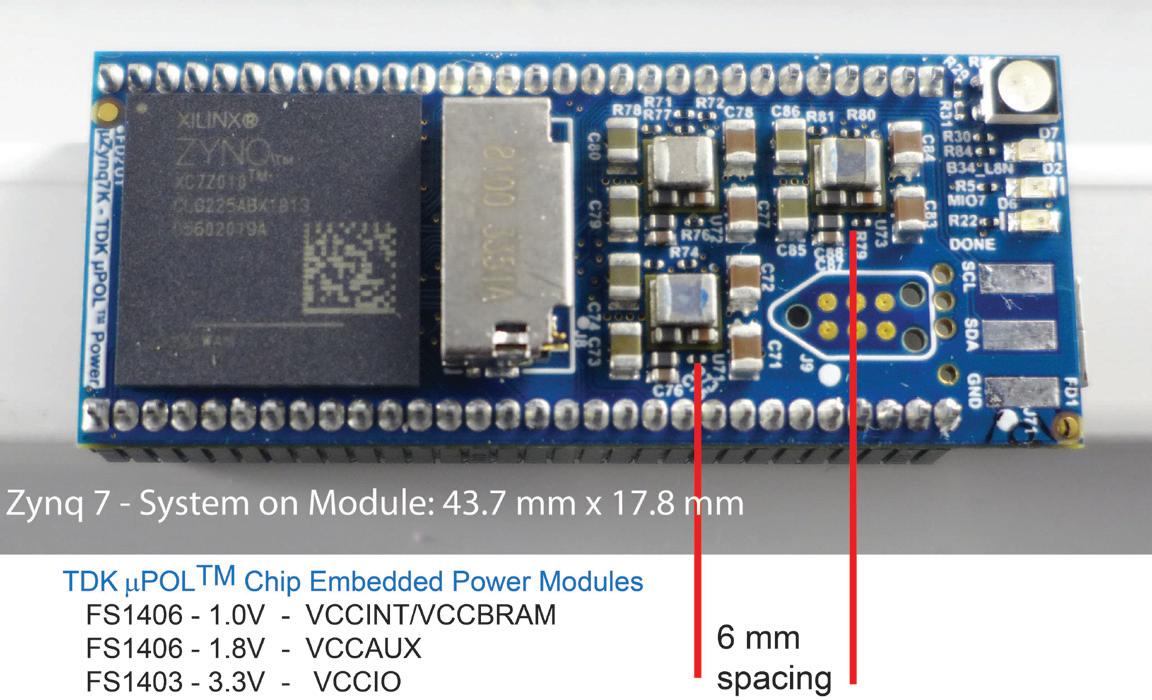

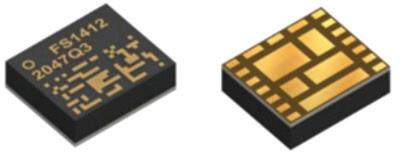

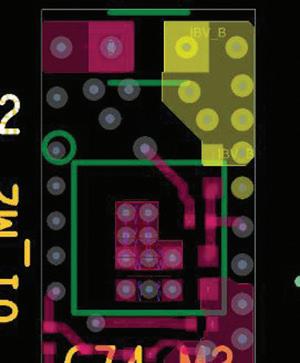

The recently announced μPOLTM power modules (see Figure 1) incorporate power circuitry built directly into a substrate to create a module that can be mounted on the front or the back of a PCB. FPGAs, SoCs, and ASICs can be mounted (as usual) nearby, and yet have shorter interconnect paths leading to better performance.

This approach has achieved 1 watt per cubic millimeter and a 15W in 49 mm3 (a typical solution with output capacitance). This technology enables the designer to achieve the highest power density in the smallest space while providing all three target benefits — power, size, and ease of use.

There are reference layouts for the most commonly used FPGAs, several Arm-based processors, and SoC (system on chip) solutions from different manufacturers. The technology behind TDK’s micropower modules is fully scalable, enabling designers to feel confident in their product roadmaps.

Ease and speed

When designing with μPOL, a designer needs only specify input capacity, output capacity, and voltage divider, then match requirements

to an available μPOL product. That is admittedly an over-simplification — but not by much. A significant amount of engineering and support resources have ensured that this technology can handle a high level of design complexity.

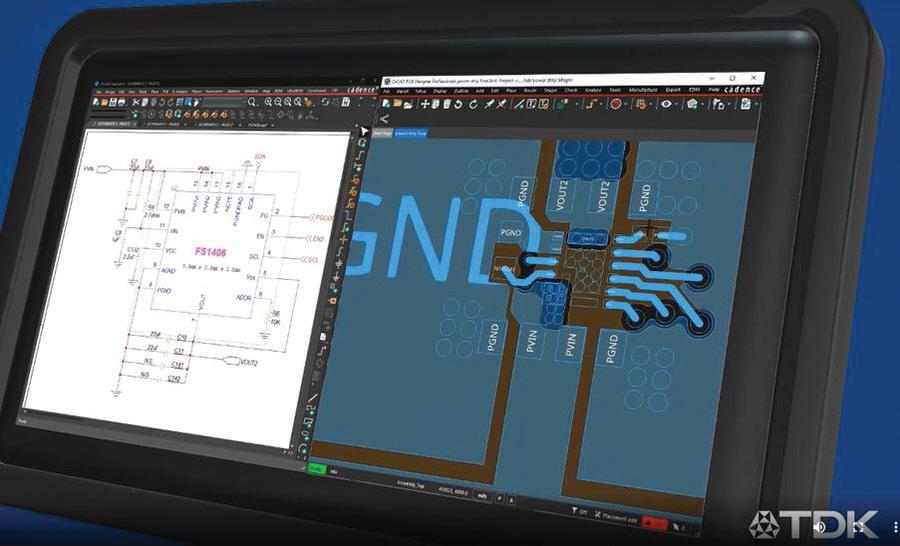

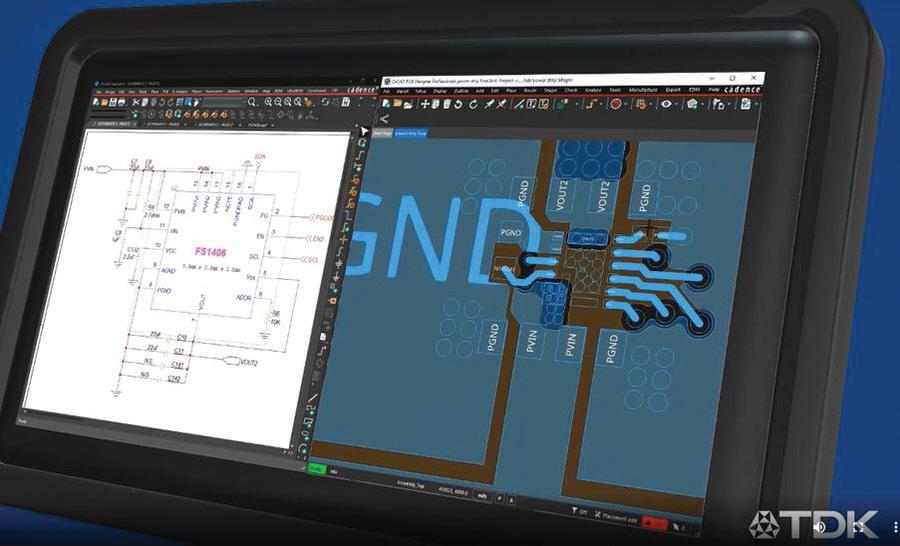

The micropower modules range from 0.6 V to 5 V output voltage, covering most designs for communication infrastructure applications, data computing, IoT, embedded vision, real-time signal processing with FPGA, robotics, and AI. Layout files that cover most of the FPGAs used in these applications are provided. Registered users can access the layouts free through Ultra Librarian, the online PCB CAD library; Cadence, Altium, Mentor, and Eagle.

16 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 1. TDK’s μPOL power module

Figure 1. Example of an OrCAD starter design layout

µ POL DC-DC product group, TDK

POWER ELECTRONICS HANDBOOK

Figure 2. TDK’s μPOL power module product line. The maximum output voltages are dependent on the maximum output currents.

Following schematic guidelines and adhering to the suggested layouts will, in most cases, save board space, minimize the bill of materials, and allow for easy and quick design completion.

The path to power density

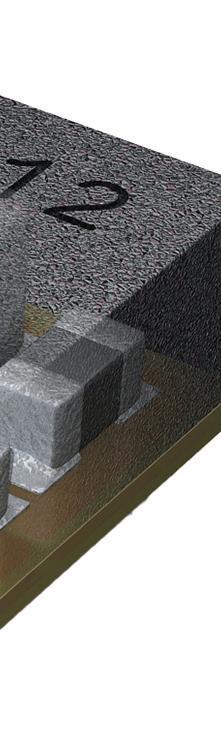

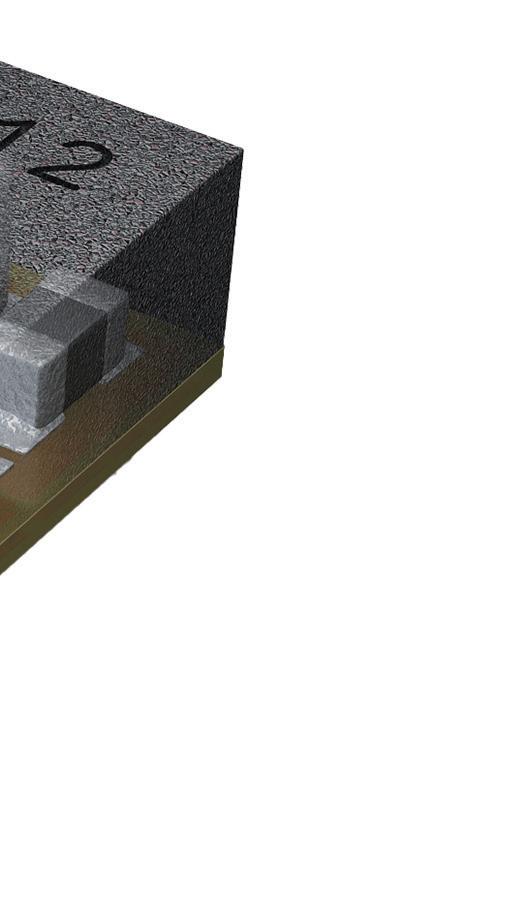

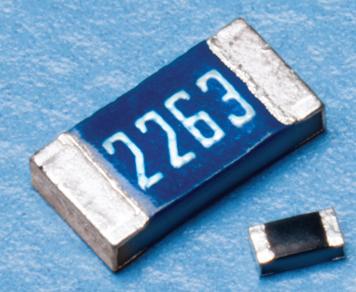

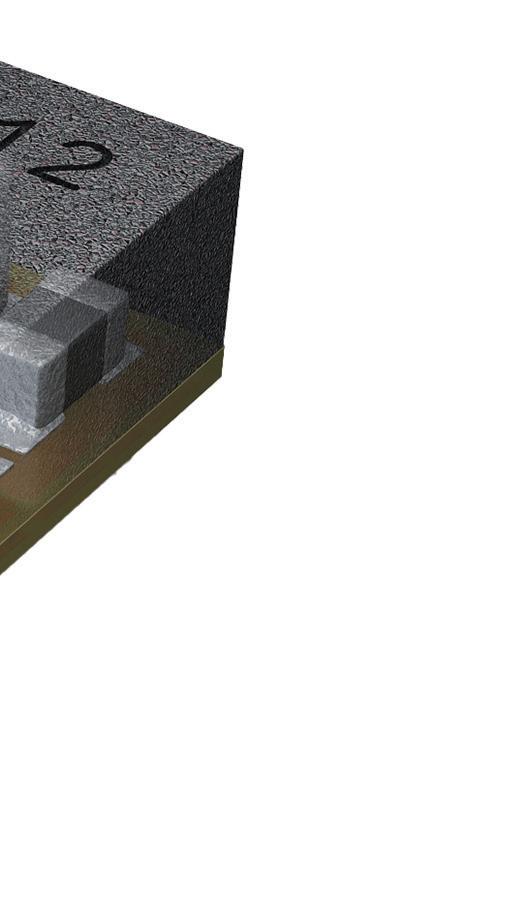

The micro power modules are based on TDK’s proprietary semiconductor embedded substrate (SESUB) technology, enabling 15 W power modules to be achieved in 3.3 x 3.3 x 1.5 mm packages, and 20 W+ modules in a 5.8 x 4.9 x 1.6 mm package.

Usually, high power density typically comes with thermal constraints. To overcome those

constraints, these modules integrate a chip-embedded IC, monolithic in that it comes with a DC-DC regulator, MOSFETs, and driver. A copper heat plate is added to the die, and a chip is embedded for optimal thermal flow from the die to the package, achieving as much as 4x to 8x better thermal design than competitive technologies. This assembly is incorporated directly into a four-layer, 300-micronthick substrate.

This substrate has no wire bonds. Wire bonds introduce parasitic losses, and as integration has progressed over the years, the problem has inexorably grown more severe, making it increasingly more difficult for designers to

DESIGN FOR HIGH-POWER DENSITY

applications such as drones.

space bonds and deal with the thermals. This, in turn, complicates the interconnect. The additional benefit of the chip-embedded

Because the thermal sink is positioned on the bottom of the SESUB, heat flows directly into the board, leading to substantially better thermal flow and minimizing the space necessary for the modules. With inductors, bootstrap, and Vcc capacitors are integrated, this architecture also allows the unique capability of full-rated current implementations

approach is high reliability — critical for shock and vibration prevalent in industrial and mobile

without the need for external air flow and output current deratings.

The layouts TDK has prepared for the most commonly used FPGAs and several processors include recommendations for output capacitors that will work best with each design.

Designing-in

Designers start the process by identifying each power rail’s voltage and maximum current requirement. The power map will indicate which power module is the best choice for each targeted voltage rail. A power map can additionally show where common modules can be used in multiple locations on the same design to help reduce costs through economies of scale.

Some voltages overlap values between modules. If there is a choice, the maximum current required for each power rail will determine the choice of module.

17 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com TDK μPOL™ Model Output voltage A max Dimensions W rating FS1403 3.3 - 5V max 3A max 3.3x3.3x1.5mm 15W FS1404 .5 - 3.3V max 4A max 3.3x3.3x1.5mm 15W FS1406 0.6V – 2.5V max 6A max 3.3x3.3x1.5mm 15W FS1412 0.6V – 1.8V max 12A max 5.8x4.9x1.6mm ~21.5W LGA / 17PIN LGA / 22PIN

Figure 3. Example power design schematic from Ultra Librarian.

Figure 4. TDK mPOL with Xilinx SoM shows a tight power design.

When in analog mode, voltage programming for devices is not required. In this case, a simple change of a resistor is all that’s needed to set the desired output voltage accurately.

Design tools

Multiple design tools are available to engineers, making the design process easier and faster. Information found here shares links to starter power schematics and PCB layout templates in Ultra Librarian, as well as links for:

• Xilinx Artix, Spartan, and Zynq FPGAs

• Intel Cyclone, Arria, and other FPGAs

• Microchip PolarFire FPGAs and SoC FPGAs

These designs address each of the key power rails, recommend the best module for each power rail, and provide a solution tested by both TDK and the FPGA supplier.

In addition to FPGAs, there are starter power schematics for other communication processors and Ethernet chipsets:

• Marvell Armada and Cavium Octeon Arm processors

• NXP LayerScape QoriQ Arm processors

• Broadcom Ethernet controller

• Intel Ethernet controller

• Marvell Ethernet PHY

Selecting components

Once the starter schematic has been chosen, the designer must determine the required input and output capacitors. The capacitors provided in the baseline solutions address typical requirements and, though they have margin built in, still need to be thoroughly evaluated if Vin is noisy or unstable and/or if Vout supplies a high transient load.

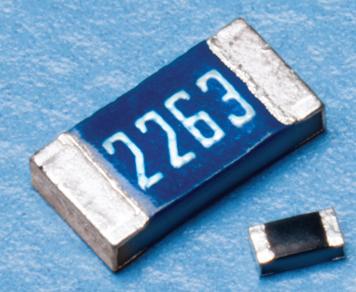

It remains the responsibility of the designer to determine the actual capacitance needed (bulk capacitance for energy storage), the type of capacitor technology to be used, and the allowable parasitic values of the capacitors, in terms of equivalent series resistance (ESR) and equivalent series inductance (ESL). These parameters are typically dictated by the transient response requirements for di/dt (change of current per change of time).

If the design requires the support of a large di/ dt transient event, additional output capacitors may be required; the type of output capacitors may need to change based on the power distribution network’s requirements for the capacitor’s equivalent ESR and ESL.

Resistor divider values should be verified for final Vout by point-of-load measurements; the designer should adjust the resistor value if needed. Due to all the output voltage options, TDK has created support tools

that include optimized standard baseline circuits with the appropriate external passive components, schematic generation, and design layouts — minimizing board space while addressing thermal considerations.

Component design and layout

Thoughtful distribution of capacitors on the output is also essential to minimize circuit board parasitics, which can impact the supply of stored energy (current) flowing to the electrical load when needed quickly.

Connections to each power plane should be kept simple and clean to ensure no lengthy ground loops are being created, or schemes that add a high level of parasitic inductance and/or capacitance. To ensure proper performance, it is recommended that the input communication pins be electrically grounded on the PCB design if I2C or PMBUS are not used in the application.

While the power modules’ current ratings do not require additional airflow, designers still need to include enough PCB thermal vias, properly designed and located, to adequately support the system power while still maintaining thermal needs (see example below for recommended designs). For example, with effective thermal via placement on the PCB, the FS1403 at 12Vin to 5V at 3A (15W at 3.3x3.3x1.5mm) requires no airflow up to 90C board ambient.

A thorough review of the proposed final thermal via solution is recommended. It is also essential to consider the copper weight on the PCB and the number of layers. Both will impact the thermal performance.

Summary

As power demands continue to rise and space becomes ever more valuable, advances in power module technology offer intriguing design opportunities. While Moore’s Law continues to prevail, power technology is moving at a similar speed, making it easier to realize its benefits.

18 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com POWER ELECTRONICS HANDBOOK

Figure 5. Layout example of the thermal vias allowing effective thermal design.

SEQUOIA & TAHOE SERIES

Precision Programmable AC and DC Sources

SEQUOIA SERIES

• Four-Quadrant Regenerative Grid Simulator with Add-On Electronic Load Option

FEATURES AND CAPABILITIES

TAHOE SERIES

• Two-Quadrant High Power AC/DC Source with Advanced Power Analyzer

• Dual Voltage ranges that support over voltage testing on 480V based systems

• 500uS time resolution for Transients

• Virtual Panels control software included

• Trigger In & Out to permit extensive coordination with external systems

• Intuitive 5” color display for ease of navigation

• Auto-paralleling for maximum flexibility with multi-chassis configurations

www.programmablepower.com 9250 Brown Deer Road, San Diego, CA 92121, USA I +1 858-458-0223

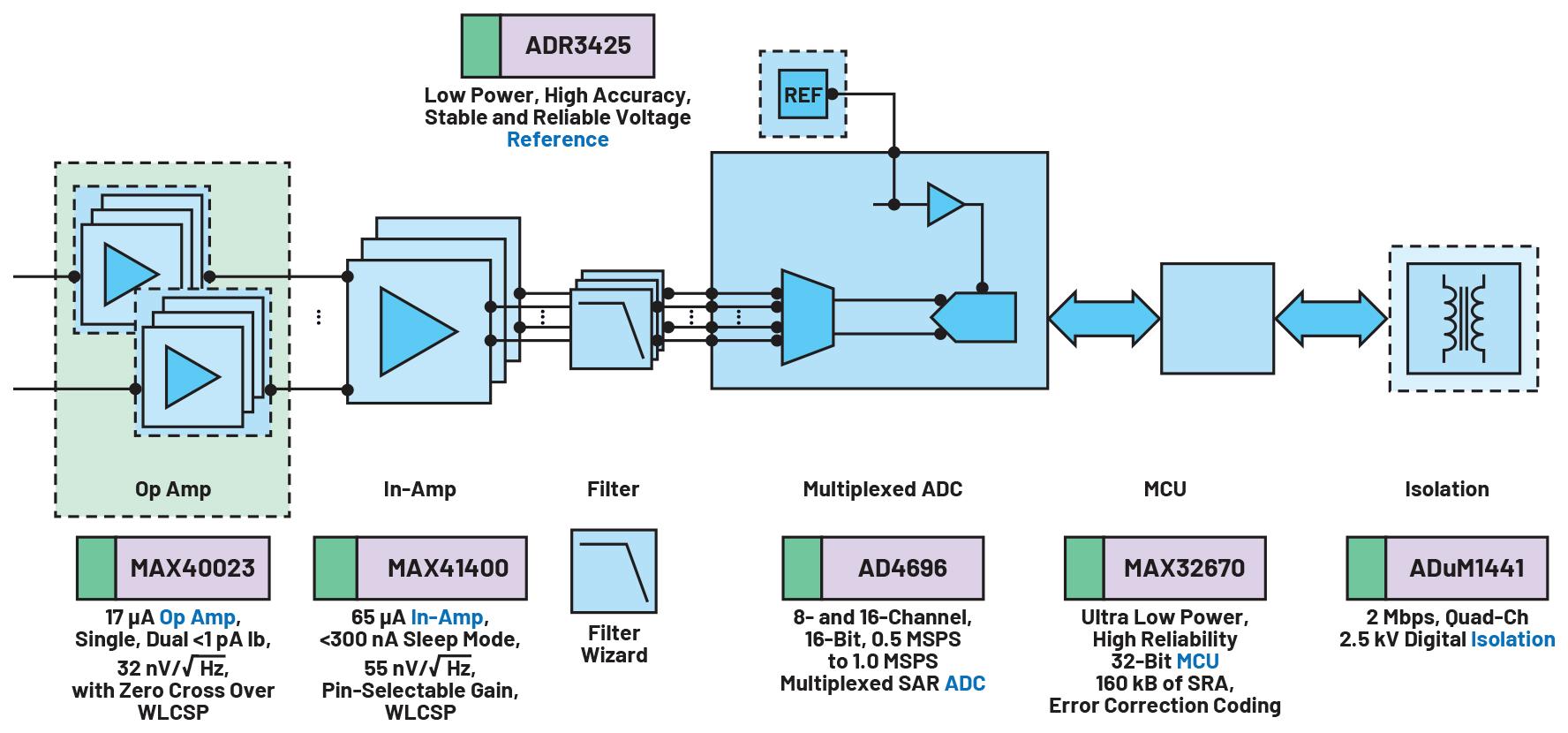

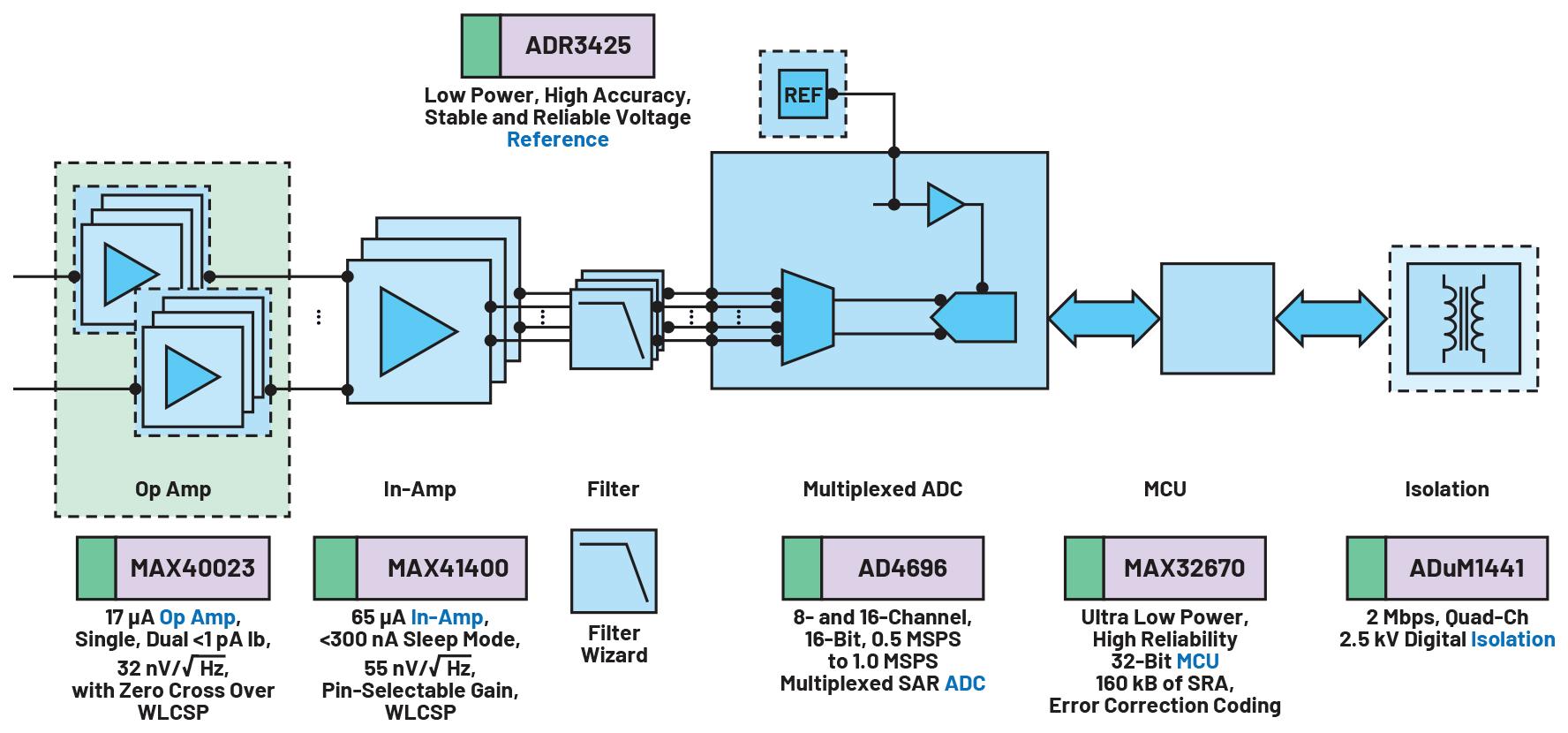

Power optimization techniques for low-power signal chain applications

Several system-level techniques are available that can make signal chains designs more power efficient and reduce system design complexity.

Low-power

signal chains

are critical when designing a batterypowered measurement system for applications such as field instruments (sensing temperature, pressure, or flow) or remote vital sign monitoring devices. Even for mains-powered systems, minimizing the environmental impact of the energy costs pushes hardware designers to improve system power efficiency. A low-power design may have indirect benefits, like smaller solution size, if enabling to reduce the number of battery cells in parallel. A further advantage of the low-power design is the lower IC die temperature due to the lower energy the system consumes, thereby extending product lifetimes.

Precision low-power signal chains are a great starting point for quickly getting a low-power hardware design done. Beyond choosing low-power components, several power optimization techniques, such as power scaling, power cycling, and duty cycling, can be implemented to reduce the system’s power consumption further. Also, design choices like appropriate resistor values or memories can be a excellent differentiator for achieving stringent lowpower targets and optimal battery life.

For example, identifying building blocks in the signal chain that can be

eliminated or powered down momentarily when certain conditions are met makes it possible to implement low-power techniques. This will require a good timing analysis1, 2, and staging or duty cycling the operation. If several building blocks are idling for the greatest portion of the time, then these can be placed into shutdown mode or directly switched off. Note that fully power cycling a device will have some implications in terms of power and timing compared to shutdown modes when available.

Once this timing is implemented correctly, significant system-level power consumption improvements can be achieved even further by minimizing the microcontroller interaction. This will require using external or internal memories to store data while the host controller is shut down.

There are some differences in how to apply power-saving techniques at the system level, depending on the type of ADC used for digitizing the sensor information, among SAR and sigma-delta, as detailed in the following sections. Also, hardware design decisions like digital comms pull-up/pulldown resistors, resistive dividers, and gain setting resistors will make a difference in the overall signal chain power consumption.

Pin naming may vary from device to device. For consistency, we will refer to AVDD for analog supply, VIO for digital supply, and VREF for reference voltage.

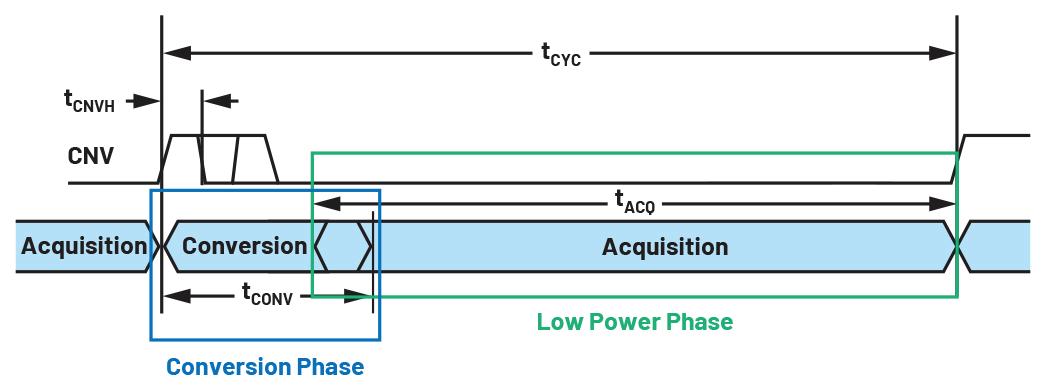

Power optimization on a SAR ADC-based signal chain SAR ADCs perform conversions on demand — that is, they toggle from sample mode to hold mode after the assertion of the CONVERSION START

Lluis Beltran Gil, Analog Devices

Lluis Beltran Gil, Analog Devices

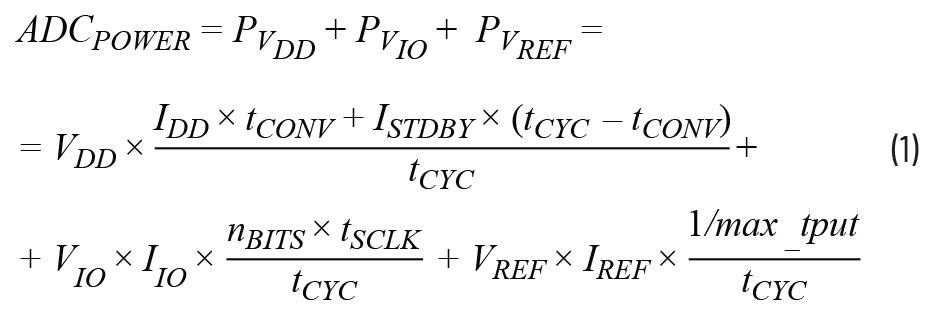

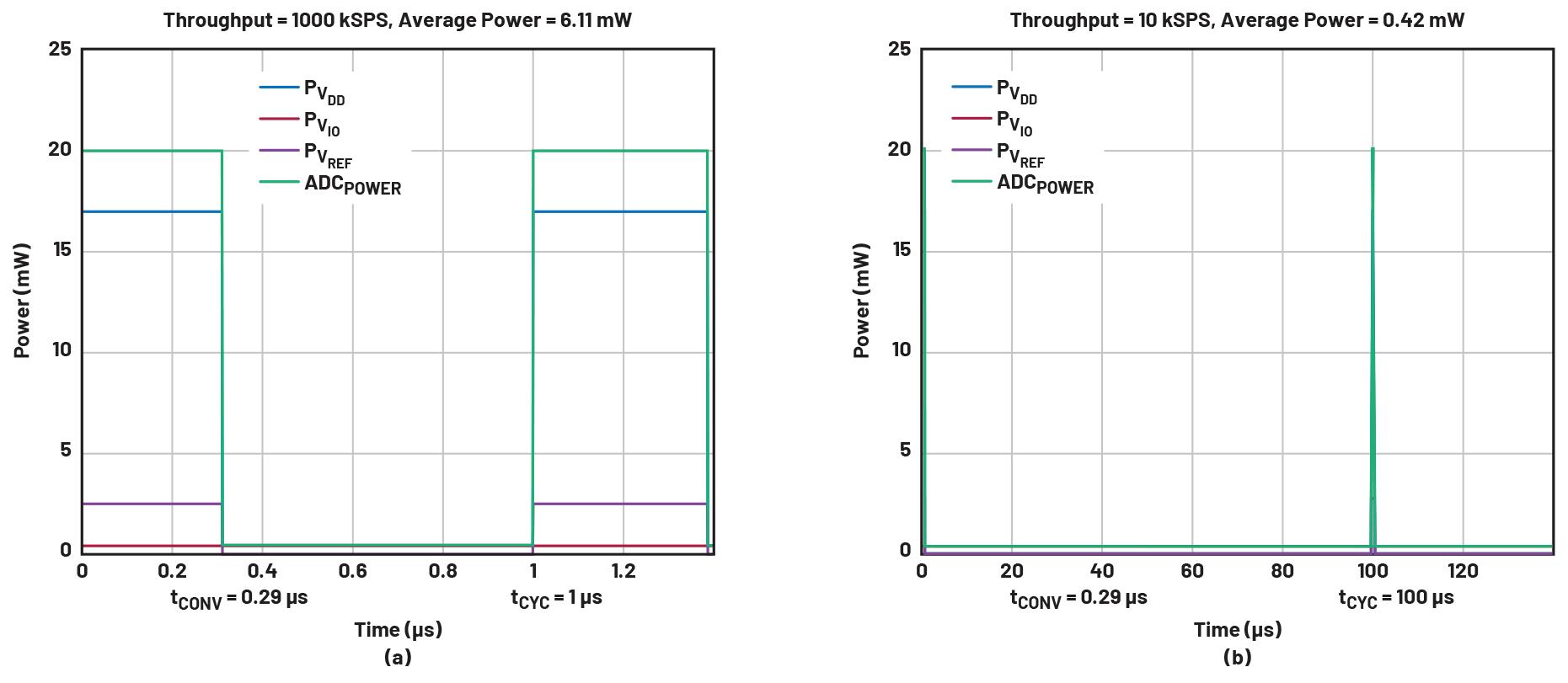

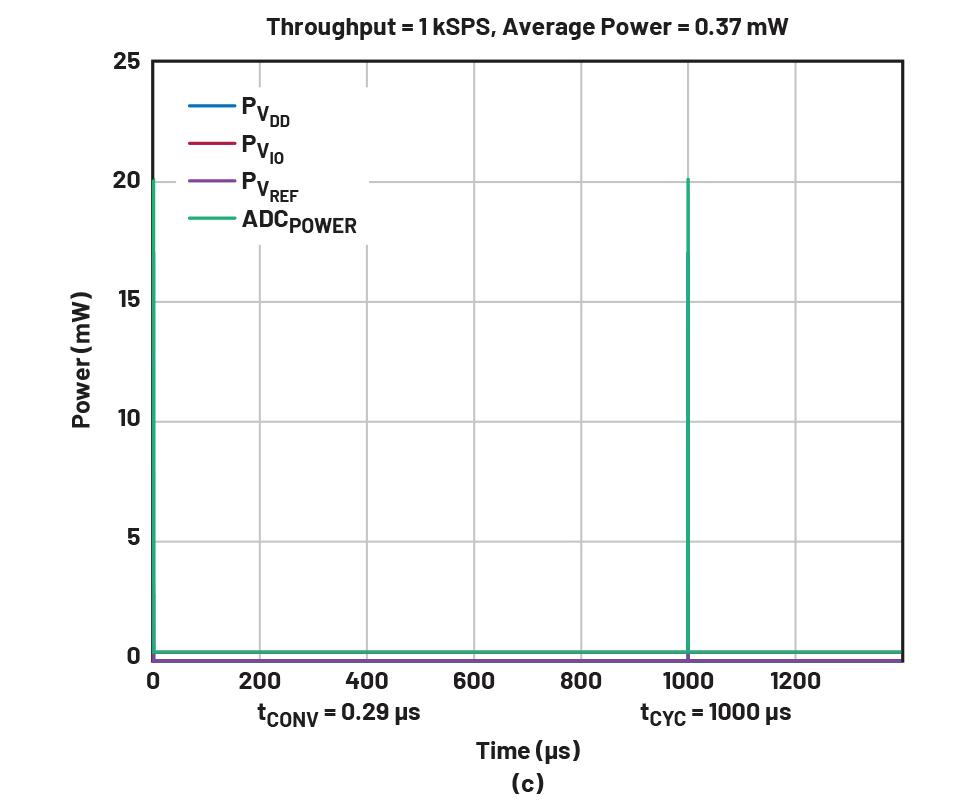

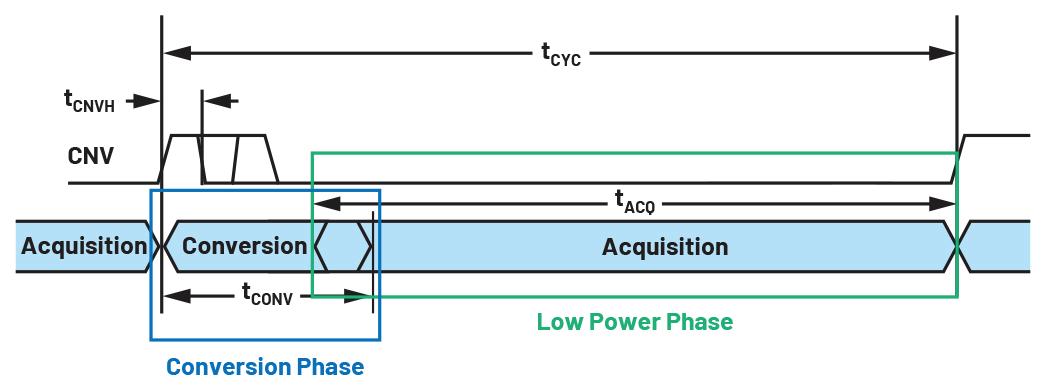

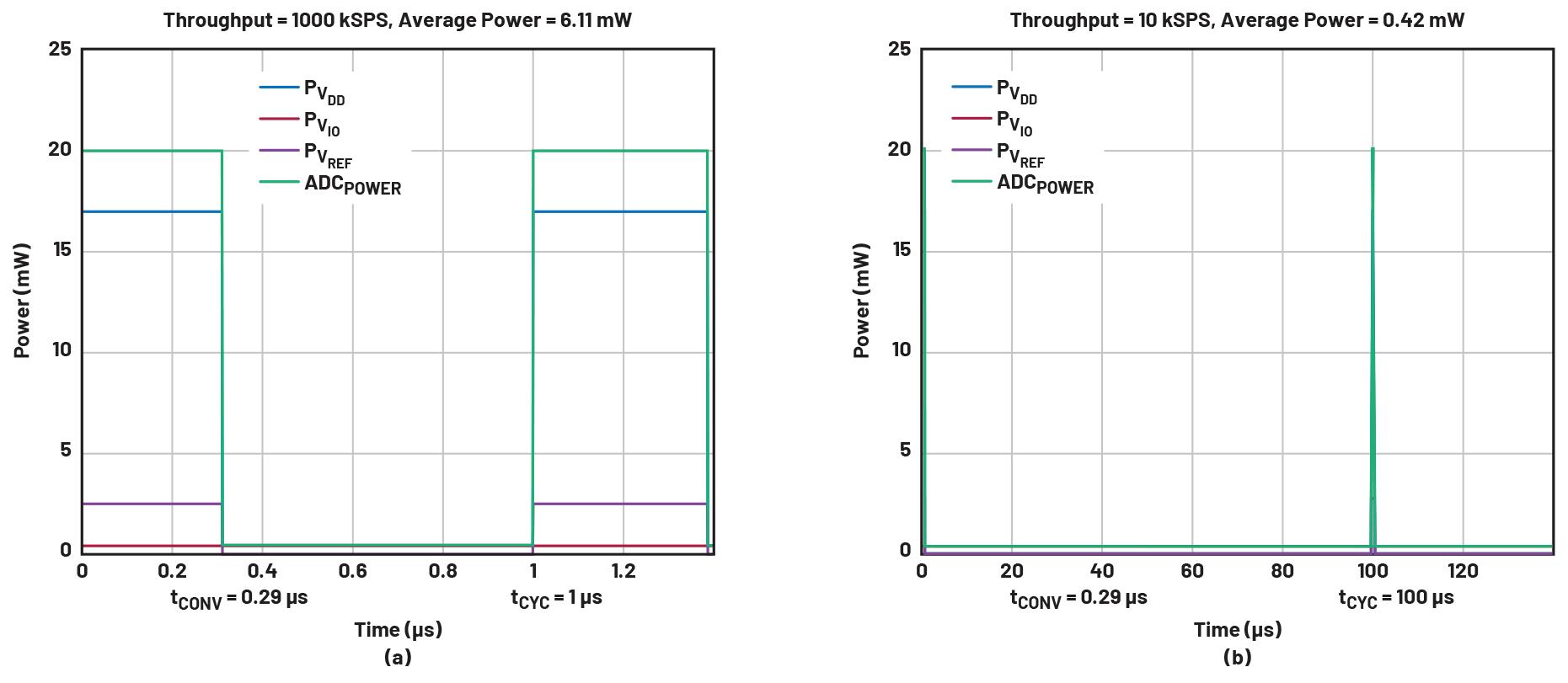

command. The conversion process starts, and once completed, it toggles back to sample mode to acquire the signal. SAR ADCs, like the AD4001 converter used in the signal chain shown in Figure 1, consume most of the power during the conversion phase, whereas consumption is minimal during the acquisition phase, as shown in Figure 2. So, despite being capable of throughputs as high as a few MSPS, power can be significantly optimized by running these converters at the minimum speed required by the application.

SAR ADC: power scaling with throughput

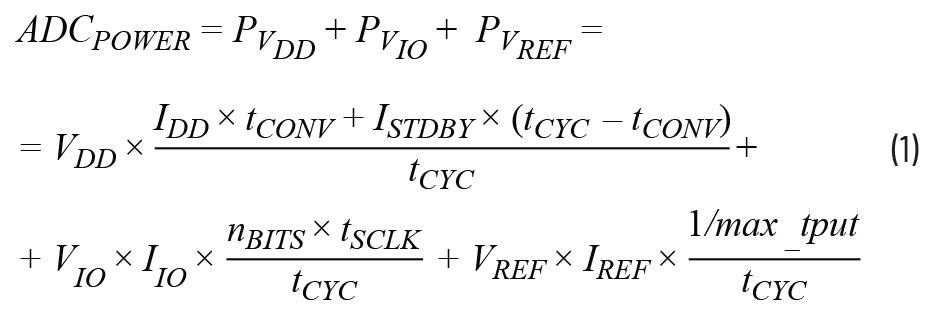

In many low-power applications, sensor information is not needed continuously but at much lower rates — on the order of kSPS or tens of kSPS. In these cases, power consumption of the SAR ADC can be scaled down with throughput, both for analog and digital supply rails.

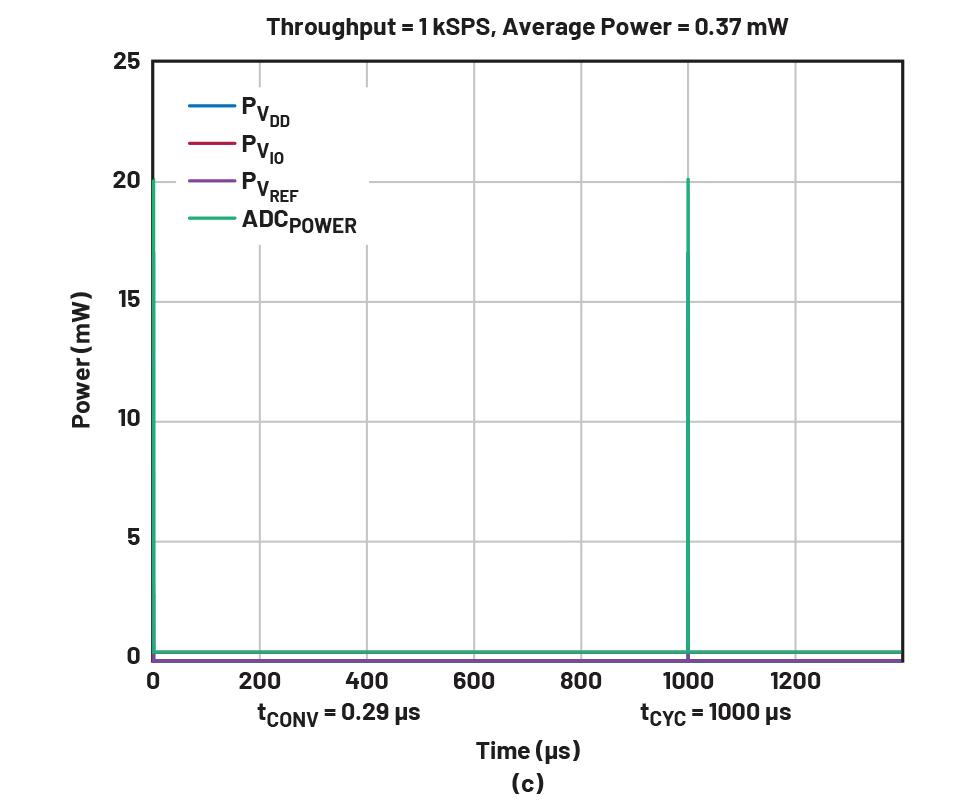

Most precision SAR ADCs have an internal clock that manages the conversion process, so the conversion time (tCONV) is fixed. With tCONV being set, the lower the throughput and the longer the cycle time (tCYC), the longer the acquisition time (tACQ), the period where the ADC minimizes its power consumption. In other words, the lower the throughput rate, the lower the power consumption per sample acquired.

Conversions are triggered externally through a digital signal so that the conversion speed can be tightly controlled. A slower sampling rate results in a longer acquisition phase and, therefore, a lower average power consumption. This can be observed in

20 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Table 1. Common Sampling Frequencies at Different End Applications

Application Common Sampling Frequency Field Instruments 60 SPs to 600 SPS Condition-Based Monitoring 1 kSPS to 10 kSPS Vital Sign Monitoring <1 kSPS POWER ELECTRONICS HANDBOOK

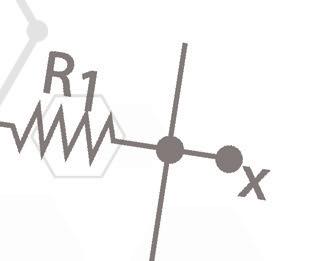

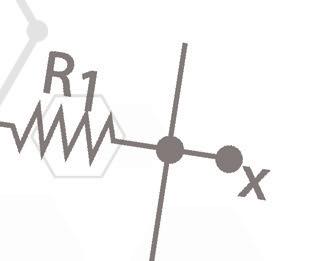

Figure 1. Single-channel voltage, current measurement in SAR ADC signal chain.

Equation 1:

Where:

tCONV is the conversion time

tCYC is the inverse of the sampling rate

VDD is the analog supply

VIO is the digital supply

nBITS is the resolution of the ADC

tSCLK is the serial clock period time (1/fSCLK)

VREF is the reference voltage, and IREF is the current at maximum throughput (max_tput)

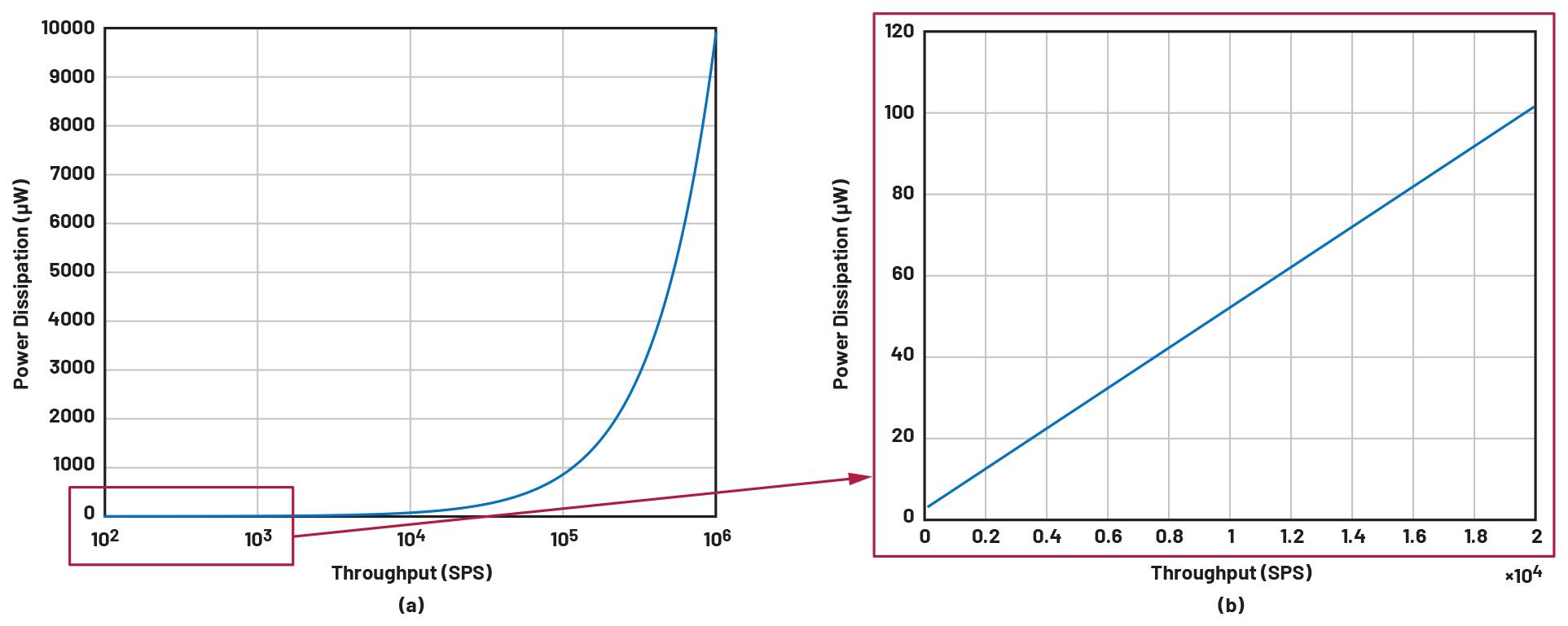

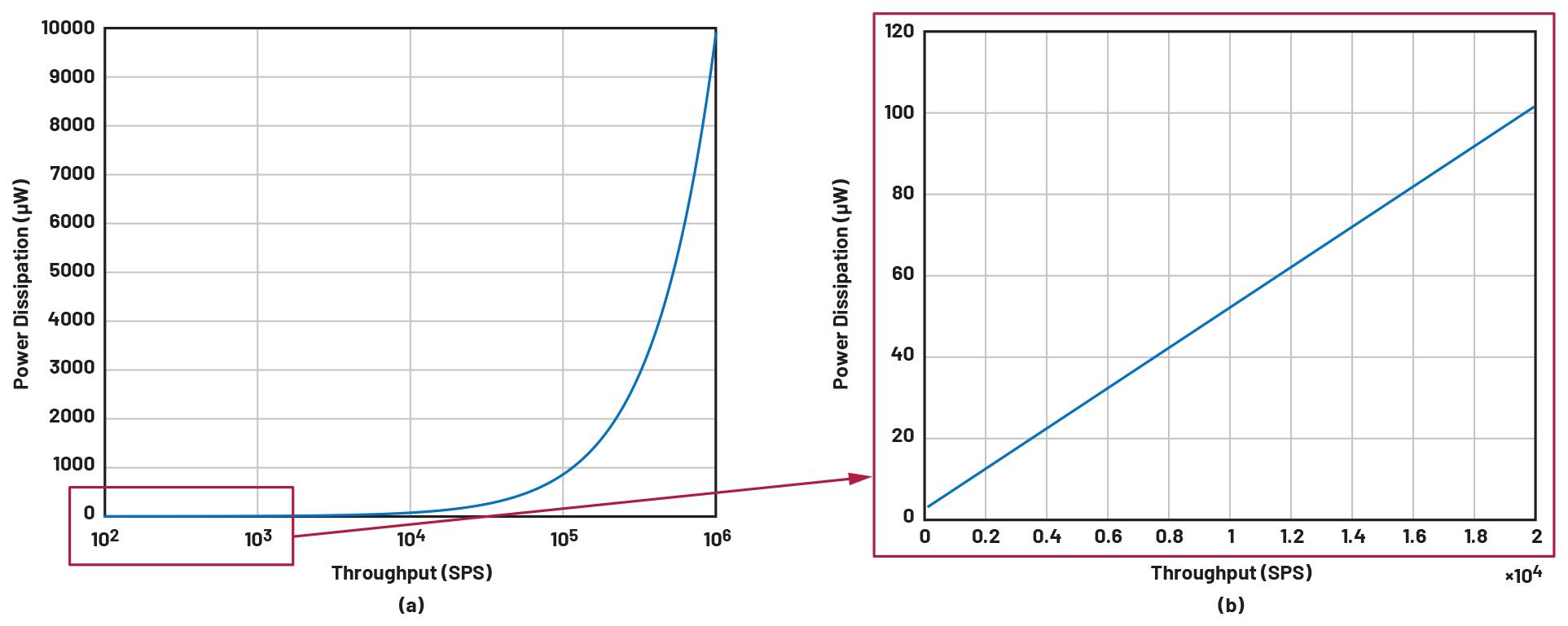

The ADC average analog power consumption will be inversely proportional to the sampling rate — according to Equation 1 and as seen graphically in Figure 4 — if tCYC is extended while tCONV remains constant.

The power consumption of the ADC shown in Figure 1 is dominated by the analog supply during its conversion phase, as shown in Figure 2. For example, in a strain gauge sensing circuit, the data acquisition rate can be as low as 1 kSPS, which reduces power consumption by 20-fold compared to running the AD4001 at maximum sampling speed. A graphical representation of Equation 1 shows how the power increases exponentially with throughput, as shown in Figure 4.

Reducing the ADC sampling rate results in a longer acquisition time, which reduces the bandwidth requirements of the ADC driver amplifier, allowing a larger base of devices to choose from. Lower bandwidth amplifiers tend to have comparatively lower quiescent current. Lower ADC sampling rates lower not only ADC power consumption but also lower power requirements for companion amplifiers.

POWER OPTIMIZATION TECHNIQUES

However, selecting a lower bandwidth operational amplifier has its trade-offs. The lower bandwidth means a lower quiescent current (IQ), but it comes at the expense of increasing the voltage noise density (eN), as shown in Table 3. As a rule of thumb, lowering the quiescent current implies that the noise density increases at a ratio of 1/√IQ. However, note that the rms noise will be filtered by the adjusted bandwidth. In other words, a hardware designer might trade off power consumption (or battery life) vs. rms noise performance for the given sample rate, amplifier, and RC net bandwidth.

Furthermore, the feedback resistors used to set the operational amplifier gain will also impact power consumption: the larger these resistors are, the less power they will consume. This, again, comes with a noise trade-off as larger resistors generate more noise. A good design practice is to make the resistors as large as possible but not large enough that their contribution to the total noise is substantial. As individual noise contributions are root sum squared for obtaining total noise, following a common rule of thumb would lead us to set a maximum limit for resistor noise

(a) avg. power = 6.1113 mW at 1 μs, (b) avg. power = 0.93756 mW at 10 μs, (c) avg. power = 0.36845 mW at 1 ms.

rms of 1/3 of that of the op amp to keep their noise contribution less than 5% of the total. This would keep the op amp noise dominant. In some applications where lowfrequency input signals are sampled at low throughput rates (a few kSPS), like the ones shown in Table 1, the driver amplifier could be removed, if no signal conditioning, like a gain stage or low output impedance, is needed. In higher-speed applications, newer ADCs like the AD4000 or AD4696 families offer high input impedance (high-Z) modes that allow lower bandwidth (and lower power) amplifiers to drive the analog inputs, sometimes even eliminating the driver. Removing this op amp will also minimize total power consumption by eliminating its contribution, as indicated by the blue bar portion shown in Figure 5. This results in significant power savings compared to traditional SAR ADCs that almost always require a driver amplifier. In the case of the AD4696, a 16-channel device, this power savings is multiplied by 16 times. The reference high-Z mode feature reduces the reference input current and the overall system power consumption.

21 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 3. AD4001 SAR ADC timing diagram and power consumption during one cycle. The longer the cycle time, the lower the average power consumption:

AD4001 Throughput Rate Total Power Consumption 1 kSPS 300 μW 10 kSPS 400 μW 1 MSPS 6 mW Table 2. AD4001 Power Scales with Throughput

Figure 2. An SAR ADC timing diagram.

SAR ADC signal chain: AFE dynamic power scaling

As described in the previous section, SAR ADC power consumption inherently scales with sample rate, but this is not true for other signal chain components. Amplifiers and voltage references consume constant quiescent current while they are powered up. Power cycling these components between ADC samples reduces the average power consumption of the signal chain. Waiting for signals to be settled on every power cycle limits the time left for powering the system on and off. This is well explained in “What Are the Most Important Timing Factors for Low Power Precision Signal Chain Applications? Part 1”and “What Are the Most Important Timing Factors for Low Power Precision Signal Chain Applications? Part 2”(although an accurate analysis for each particular signal chain design is recommended).

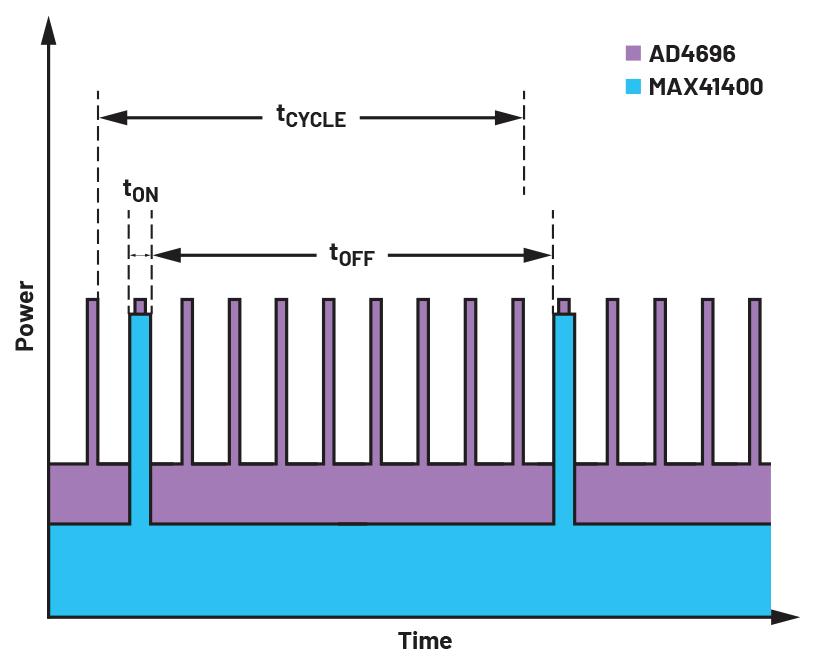

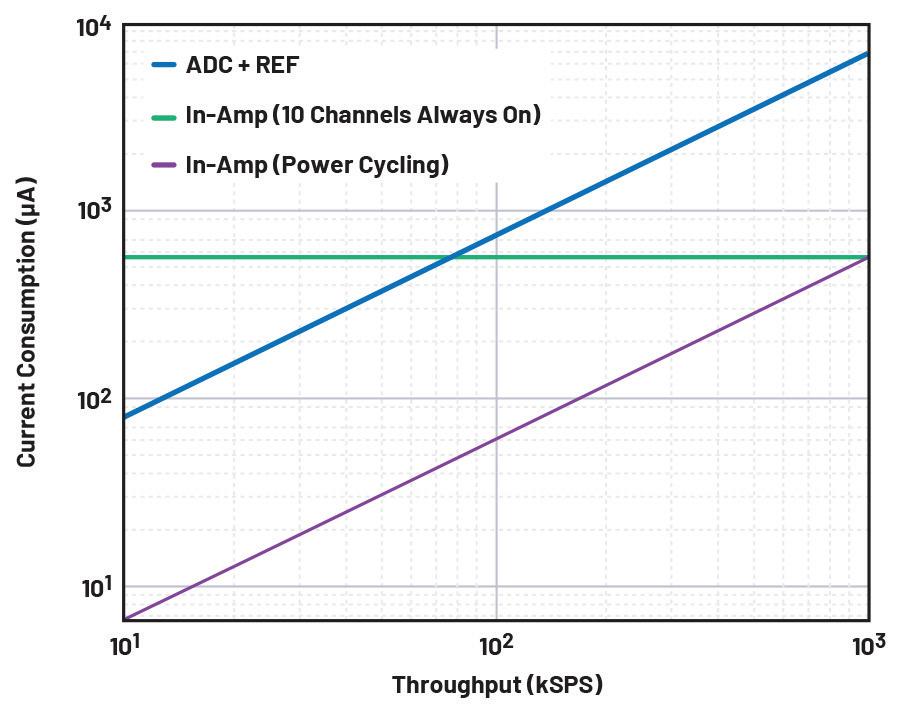

Using highly integrated ADCs, with more analog front-end (AFE) blocks on chip, enables faster power-up and power-down transitions without compromising the performance. However, in many scenarios, a design may use discrete components for optimal performance. An example is shown in Figure 6.

This signal chain is multichannel and is comprised of one MAX41400 plus one antialiasing filter per channel, feeding into a 16-channel SAR ADC (the AD4696) with an ADR3625 precision reference.

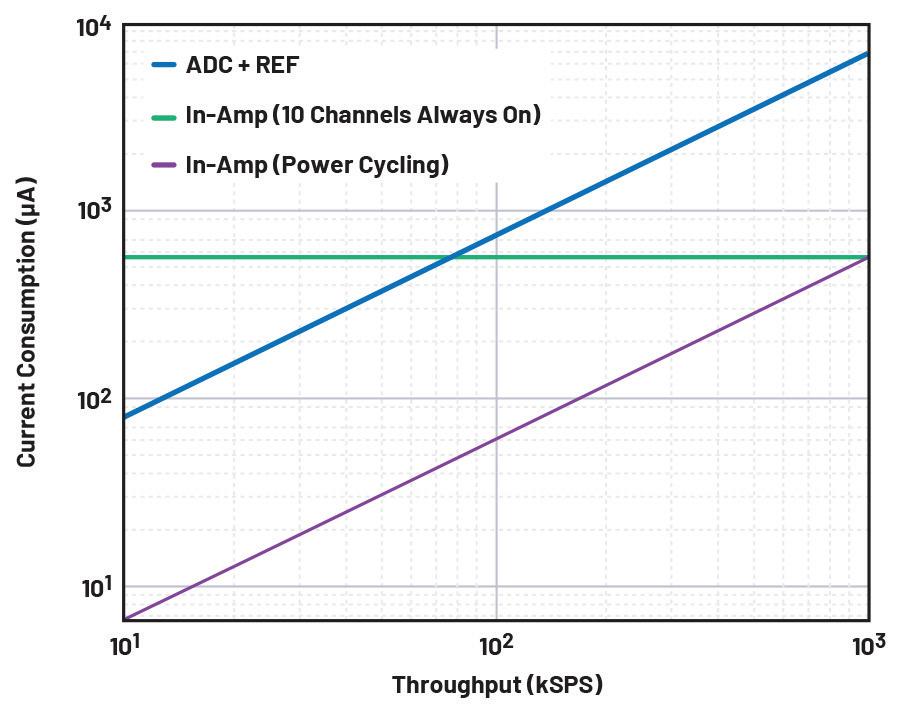

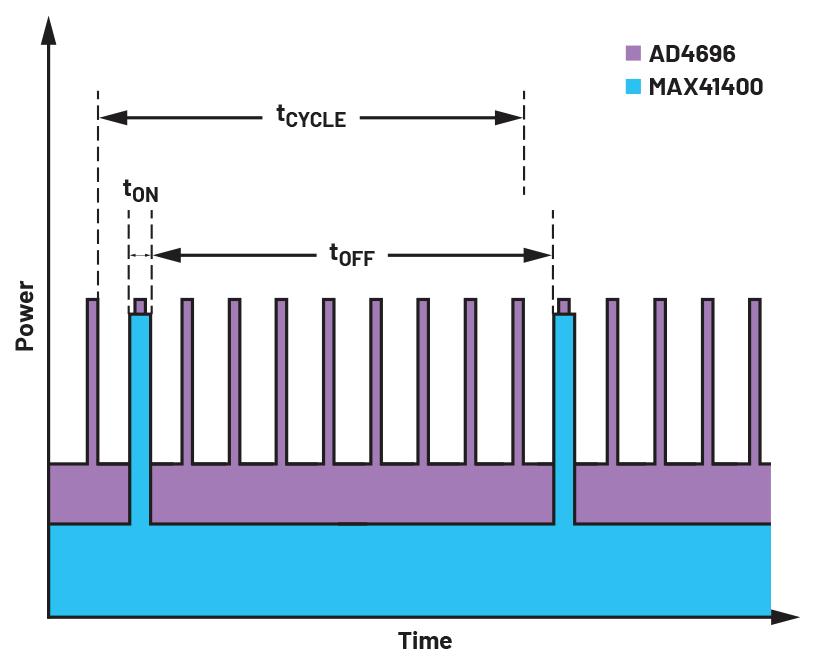

As shown in the previous section, running the ADC at the lowest acceptable throughput

reduces its power consumption. Beyond that, if the idle time is large enough, the amplifier can be put into shutdown mode during a portion of the acquisition time, given that for a multiplexed system like this, only one amplifier needs to be powered up at a time. The frequency at which the amplifier needs to be powered up is tCYC/LSEQ, where LSEQ is the length of the sequence, which is ten in the example given in Figure 7. For example, if running conversions at 1 kSPS per channel and

the higher the tCYC, and the lower the IAVG tON is the time during which the amplifier is turned on. When the ADC switches from the acquisition to conversion phase, the amplifier can be powered off, as extending tON longer than the minimum required does not yield any benefit. This off-time (tOFF = tCYC – tON) should be maximized for minimum power consumption, not to the extent of compromising SNR or THD. Finding the right timing will depend on the application, the devices used, and the throughput rates. In fact, tON and throughput are inversely proportional: lower throughputs lead to longer idle time, and longer idle time requires longer tON to power the amplifier back up. Based on the datasheet, the typical conversion time of the SAR ADC is 415 ns. This conversion time plus the 100 μs required to power up the amplifier after shutdown will add up to the minimum tON time. So, the average current consumption will be:

Compared to an amplifier that is always enabled, the shutdown modes and fast powerup time of the MAX41400 result in a 10× reduction in current consumption.

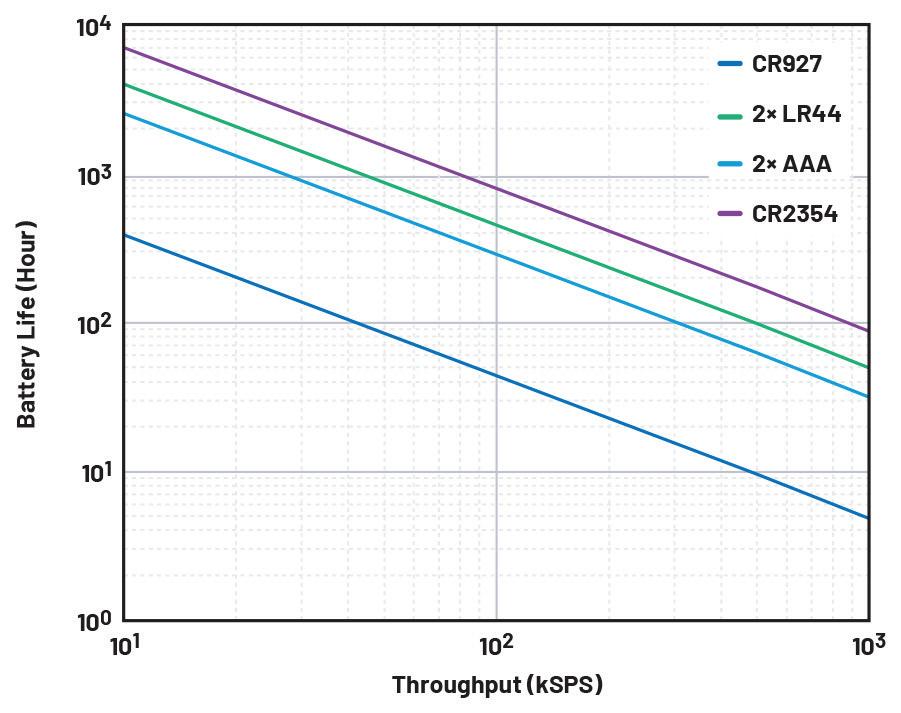

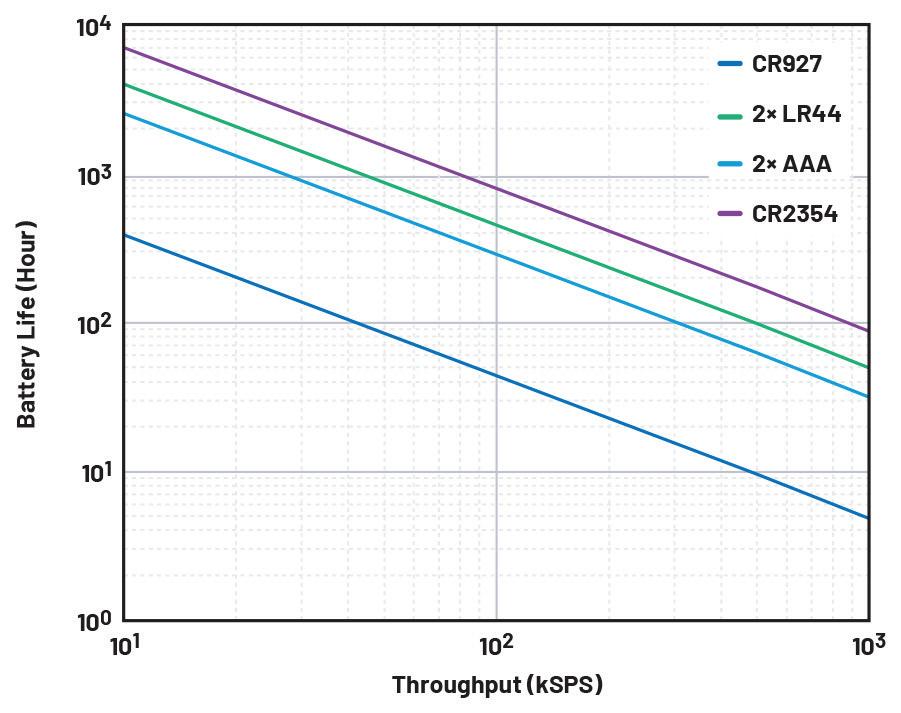

For a more general view, besides power savings calculated on the examples shown so far at a given throughput rate, all these equations can be represented graphically as in Figure 9, with the specifications taken from the data sheets (assuming reference and analog input high-Z mode are enabled).

This same analysis can be done for battery life instead of power consumption by dividing the battery capacity by the average current drawn.

In this case, the relationship is inversely proportional — the lower the throughput, the longer the battery will last.

the conversion time is a maximum of 415 ns, the amplifier on each channel can be placed into shutdown mode for around 10% of the cycle time.

The quiescent current (IQ_ON) of the amplifier is 65 μA when fully powered up, but it can be reduced to 0.1 μA when placed into shutdown mode (IQ_OFF). The average current consumed (IAVG) by the amplifier can be scaled with throughput by powering it down in between samples.

Once again, the slower the throughput,

Any amplifier, even if it does not have a shutdown mode, can be power cycled. That is, powering it on and off entirely instead of entering shutdown mode. However, care must be taken. On the one hand, the wake-up time will be longer to get the amplifier ready so that the minimum tON will be longer. On the other hand, charging and discharging the decoupling capacitors repeatedly will have implications on the current drawn to charge them up every power cycle, increasing the overall power consumption compared to using shutdown modes. Also, if the sensor is still driving the amplifier inputs while the rails are not powered up, this may lead to damage if they are unprotected.

22 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 5. Power distribution per supply rail (op amp, analog, and digital rail) at various throughputs Different amplifiers were used depending on the bandwidth needs, as per Table 3.

Op Amp Bandwidth IQ eN

90 MHz 3 mA 1 nV/√Hz

16 MHz 1.6 mA 7.3 nV/√Hz

80 kHz 17 μA 32 nV/√Hz

Figure 4. (a) AD4001’s power scaling with throughput, graphical representation of (b) zooming in for the frequency range of interest—that is, under 10 kSPS.

ADA4897-1

ADA4610-1

MAX40023

POWER ELECTRONICS HANDBOOK

Table 3. Operational Amplifier Bandwidth vs. Current Consumption and Noise Performance; Bandwidth and Power Are Inversely Proportional

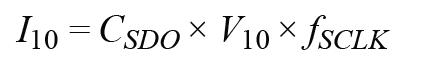

SAR ADC-based signal chain: digital supply power scaling

The previous section focused on reducing the analog supply power consumption, given it is the maximum contributor to the total power consumption. Reducing the throughput also has an impact on the digital power consumption as it allows the serial clock to run at a lower frequency:

Another point to note is the value of the pull-up/pull-down resistors used in the digital communication lines. These resistors ensure a proper logical level at the digital input/ output, and their value may impact the overall system power consumption. Using too low a resistor value, also known as strong pull-up, will cause a high current to flow through it. Hence, unnecessarily low values should be avoided. On the other end, if the resistance is too high, the voltage drop caused by the leakage current could result in the interpretation of an incorrect logic level. In addition, the voltage drop impacts the propagation. Designers must use the highest resistor value without compromising the voltage level (this will depend on the digital supply voltage and leakage current) or the signal integrity.

POWER OPTIMIZATION TECHNIQUES

Sigma-delta ADC-based signal chain

In the case of sigma-delta ADC-based signal chains, the power scaling concept described in previous sections is not applicable straight away. This is because conversions are not externally triggered; instead, they work from a free-running clock.They cannot remain idle for a certain period of time as a function of an external conversion start signal.

However, many sigma-delta ADCs feature standby modes that can be used if the ADC does not need to convert continuously. As in previous sections, timing considerations need to be considered as recovering the device from standby mode requires a wake-up time during which no samples can be taken.

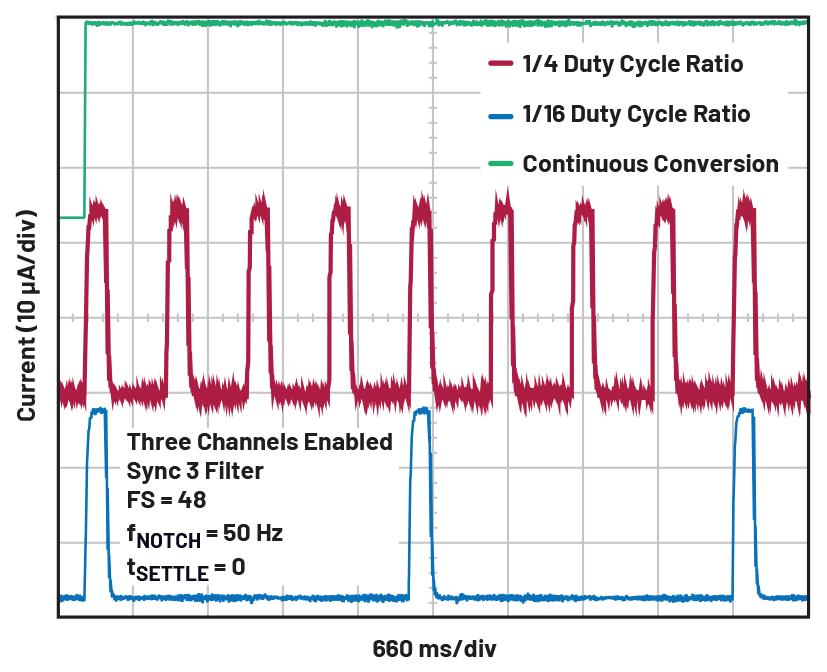

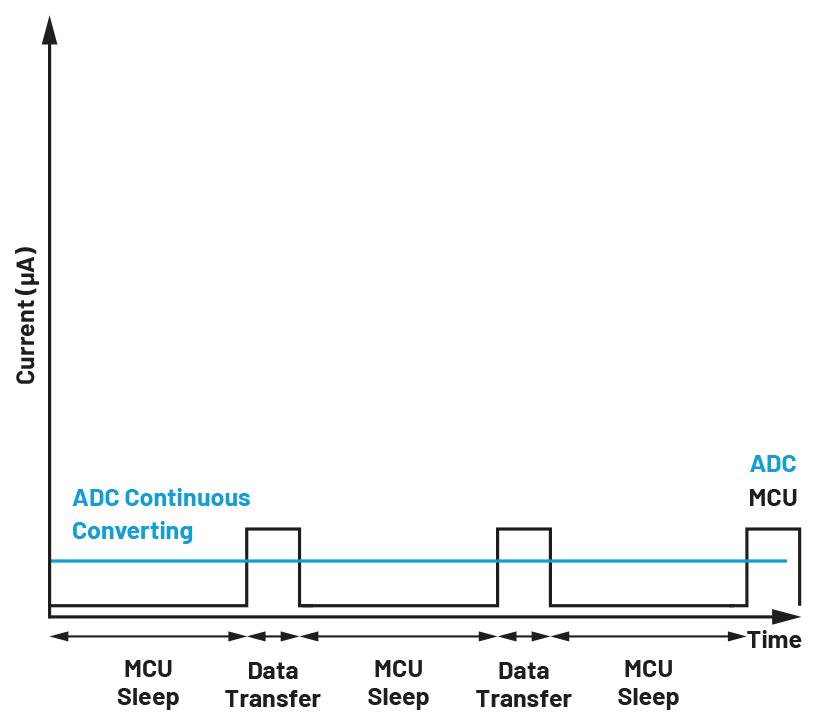

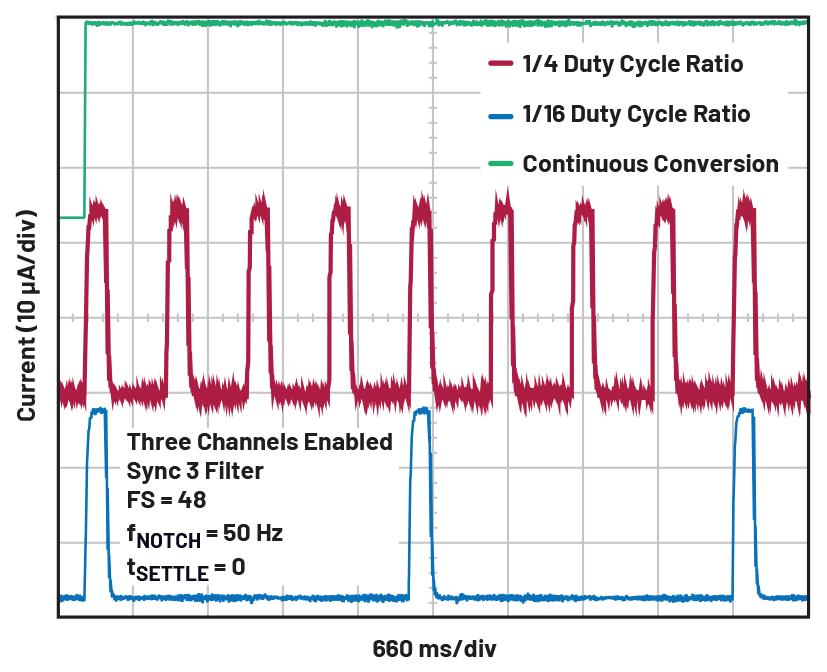

Highly integrated sigma-delta ADCs offer duty cycling and standby modes. That way, the ADC powers up and down automatically without the need to interact with the host every cycle. The AD4130 offers two modes, 1/4 and 1/16, which means it is active during 1/4

or 1/16 of the time. That leads to significant power reduction compared to continuous conversion mode, as shown in Figure 10. Depending on the required throughput rate, techniques for optimizing power consumption can be either using one of the duty cycling modes or just putting the part into standby mode for a given period. Indeed, the AD4130 has many operating modes that may impact power consumption of the ADC. The active functional model in ACE6 shows the power consumption and the expected battery life for the selected ADC configuration.

Sigma-Delta ADC-based signal chain: AFE dynamic power scaling with duty cycle

Just as with the SAR ADC-based signal chain, a sigma-delta-based signal chain can take advantage of the duty cycle to power down certain blocks when the ADC is placed into a low-power state (Figure 10). That would allow AFE power savings similar to the ones shown in Figure 9.

Sensor excitation

A complete solution provides the core converter, the internal programmable gain

amplifier, and sensor biasing and excitation (selectable current source and precision voltage reference). This integration has implications in terms of ease of use, size, and optimization on biasing, timing, or power cycling among the different building blocks. The ADC reduces the overall system power consumption by

23 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com

Figure 6. A multichannel measurement signal chain.

Battery Capacity (mAh) CR927 30 2x LR44 158 2x AAA 1000 CR2354 560

Figure 7. Power cycling the MAX41400 in a multichannel multiplexed application, based on the AD4696 ADC (assuming only ten channels are used for easier visualization).

Figure 8. Signal chain power consumption vs. throughput, with and without power cycling at the front end.

Figure 9. Battery life extends with power cycling/scaling.

Table 4. Batteries’ Capacity

housing all these blocks on chip. Furthermore, it simplifies the design cycle thanks to its flexibility in many different platforms like RTD, thermistor, or bridge sensors, to name a few. It also reduces the BOM count and the need for several power supply rails.

Other power optimization techniques

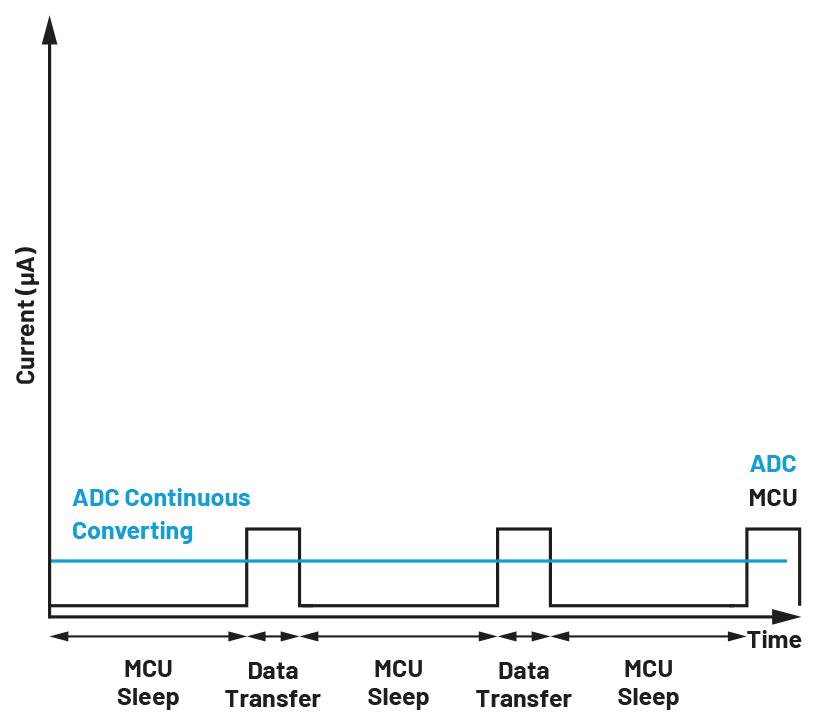

Throughout this article, several ways to minimize the signal chain power consumption have been presented. However, one portion of the signal chain has not been considered yet is the host controller. If the controller is powered up all the time because it needs to read and post-process data from the ADC, it will sink a good portion of the power. Placing the controller into sleep mode while not in use will help achieve extra power savings.

ADCs with on-chip FIFO

If the application does not need real-time data but must read data points at a much lower rate, ADCs with on-chip FIFO might play a role. The AD4130 incorporates such a block, and this FIFO can store up to 256 conversions, so if the output data rate (ODR) is, for example, 2.4 kSPS, instead of reading every 416 μs, the microcontroller can be put to sleep mode and wake up every 100 ms to read the whole data memory in one go (see

the Data Transfer section in Figure 11). In other words, having an ADC with memory that stores up to the latest 256 samples also enables power cycling of the microcontroller, thereby drastically reducing the overall system power consumption.

Streaming ADC data to memory through Direct Memory Access (DMA)

An alternative for ADCs that do not include on-chip FIFO would be to use the direct memory access (DMA) available in most microcontrollers. DMA enables the passing of data directly from a peripheral (in this case, the SPI) to memory (SRAM) without CPU intervention or interrupts for every single ADC sample received. The chosen microcontroller will have a direct impact on achievable power savings. In many cases, the microcontroller can stay in sleep mode most of the time and trigger an event only when an ADC sample is received. This event will then briefly alert the DMA to start performing the SPI transactions and to return to sleep after that, thus minimizing the microcontroller power consumption compared to having the CPU fully awake for the whole SPI transaction. Note that using the DMA is only applicable if the format of the ADC data matches the destination memory. For most microcontrollers, the DMA can be easily used only when the ADC data is 16 or 32 bits long.

Interrupt-driven programming

Many low-power applications do not require the recording and processing of every single data point but rather monitoring that the magnitude sensed is within certain thresholds. Traditionally, to do this, the host controller needed to be constantly awake to read each ADC sample and decide if the value was acceptable or not. Consequently, it would trigger an interrupt routine if need be.

Thresholds can be programmed such that a GPIO pin asserts only if the ADC output code is out of the user-defined bounds. This way, the host controller can stay in sleep mode most of the time and only wake up when the GPIO asserts, minimizing its power consumption, given it will only be active when it is necessary to perform an action.

Conclusion

When designing a battery-powered measurement system for applications such as portable field instruments, condition monitoring, or vital sign measurements (VSM), low-power signal chains are ideal for achieving poweroptimized solutions. Analog Devices’ precision low-power signal chains ease the journey for

designers building low-power measurement solutions, which offer the optimal combination of precision amplifiers, voltage references, ADCs, and isolation products. In these signal chains, power consumption is optimized while keeping noise performance, size, and ease of use as key vectors. These signal chains come in different flavors: single-channel, discrete multichannel (multiplexed), fully integrated multichannel solutions, and ready-to-go poweroptimized designs, offering an excellent starting point for low-power design.

References

Padraic O’Reilly. “What Are the Most Important Timing Factors for Low Power Precision Signal Chain Applications? Part 1.” Analog Dialogue, Vol. 56, No. 3, August 2022.

Padraic O’Reilly. “What Are the Most Important Timing Factors for Low Power Precision Signal Chain Applications? Part 2.” Analog Dialogue, Vol. 56, No. 3, August 2022.

The Data Conversion Handbook. Analog Devices, Inc., 2005.

Michael Clifford. “Fundamental Principles Behind the Sigma-Delta ADC Topology: Part 1.” Analog Devices, Inc., January 2016.

Bruce Pepitas. “Introduction to Dynamic Power Scaling.” Analog Devices, Inc., January 2016.

Analysis | Control | Evaluation (ACE) Software. Analog Devices, Inc.

Brandon Hurst. “How to Accelerate Peripheral Monitoring in Low Power Wearables with DMA.” Analog Dialogue, Vol. 56, No. 1, January 2022.

Maithil Pachchigar and Alan Walsh. “NextGeneration SAR ADC Addresses Pain Points of Precision Data Acquisition Signal Chain Design.” Analog Dialogue, Vol. 50, No. 4, December 2016.

Sanjay Rajasekhar and Arvind Shankar. “How to Leverage Input High-Z Technology to Reduce Solution Power and Size.” Analog Devices, July 2022.

24 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com POWER ELECTRONICS HANDBOOK

AD4130 Power Mode Typical Current Consumption Continuous Conversion 32 μA Duty Cycling 5 μA Shutdown Mode 0.5 μA

Figure 11. Microcontroller power reduction by using the ADC’s onchip FIFO.

Table

5.

AD4130 Current Consumption for Each Power Mode

Figure 10. AD4130 current consumption under different modes of operation: continuous conversion, 1/4 duty cycle, and 1/16 duty cycle.

REGISTRATION IS NOW OPEN

A better way to handle

dc-dc converter hold-up times

Converters with built-in holdup circuitry reduce the size and requirements for input capacitors.

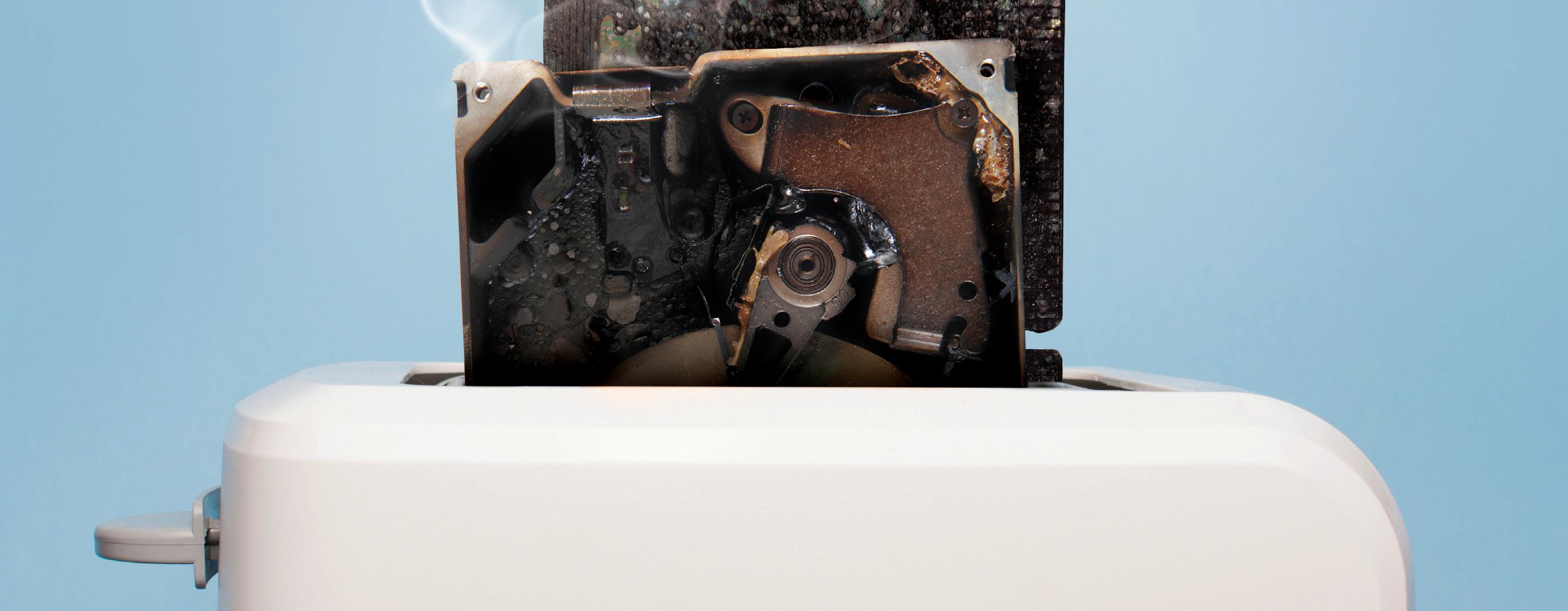

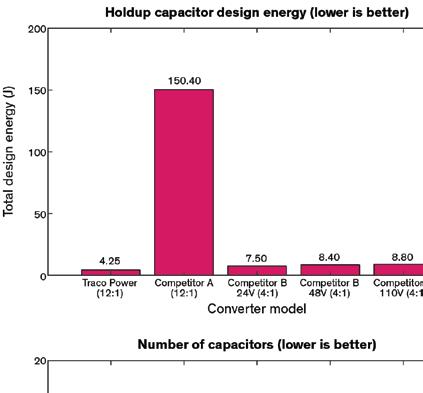

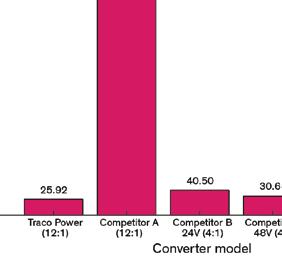

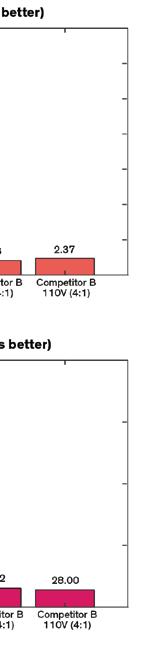

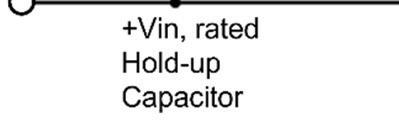

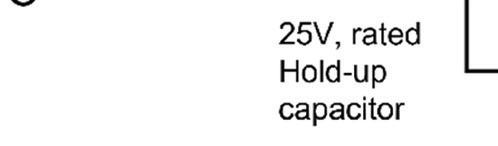

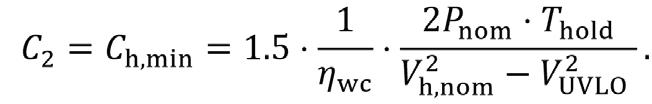

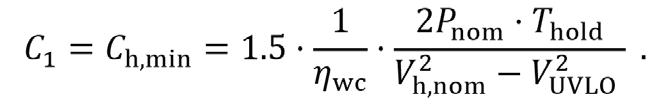

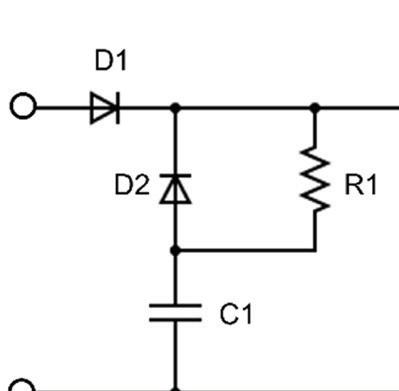

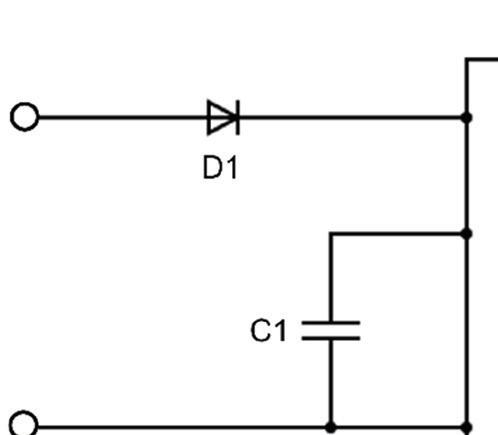

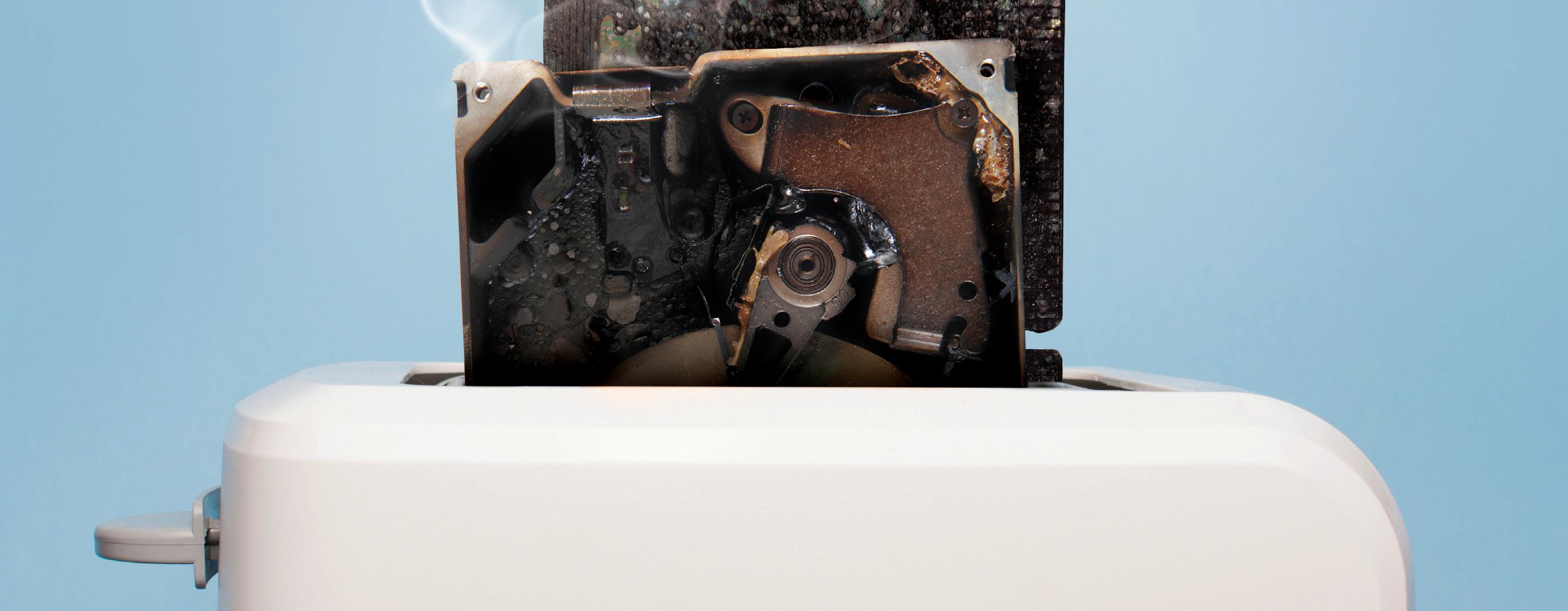

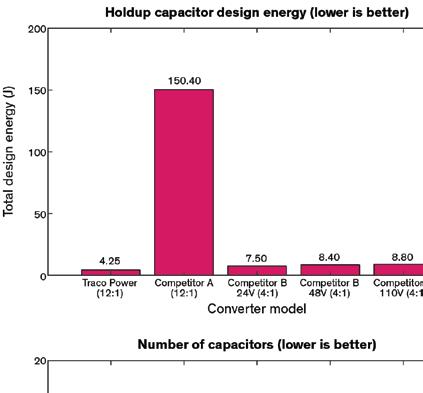

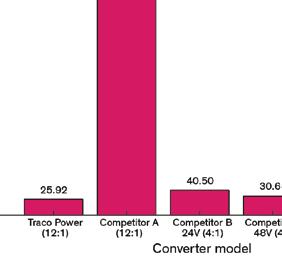

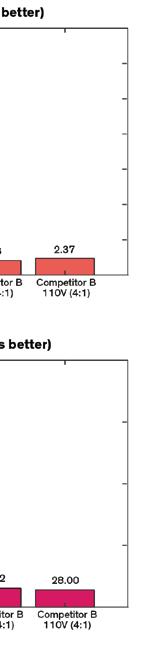

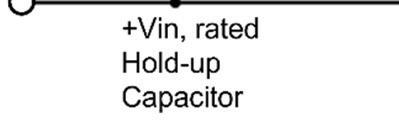

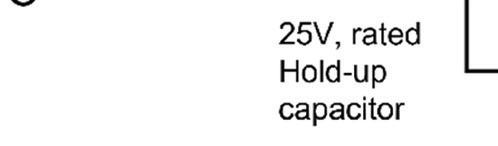

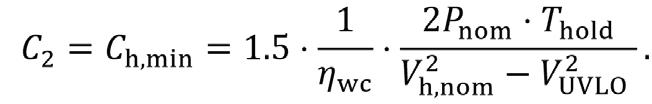

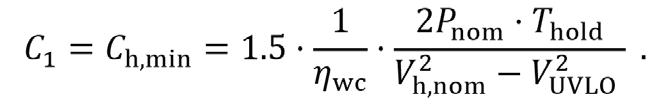

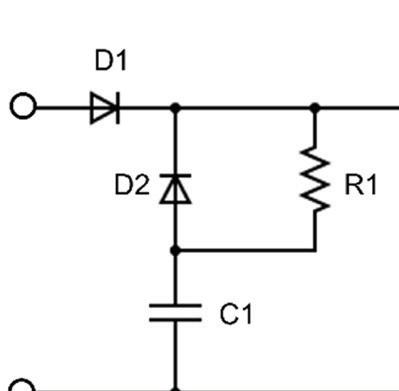

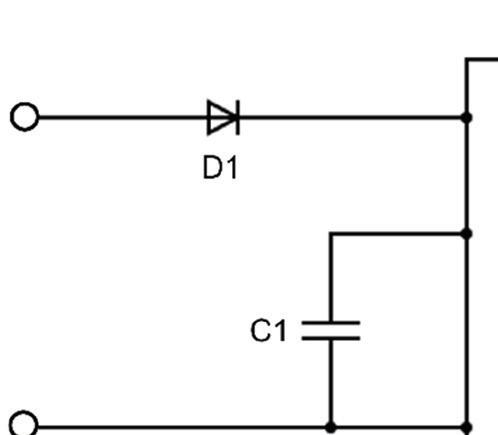

DC-DC converters are generally designed to maintain their output despite brief interruptions of their input power. The duration of this output hold-up often is set by the value of an external capacitor connected across the converter input terminals. However, some types of converters now feature a dedicated holdup capacitor connection (Bus pin). This scheme can save up to 93% on external capacitor costs while reducing their volume by up to 93% as well.

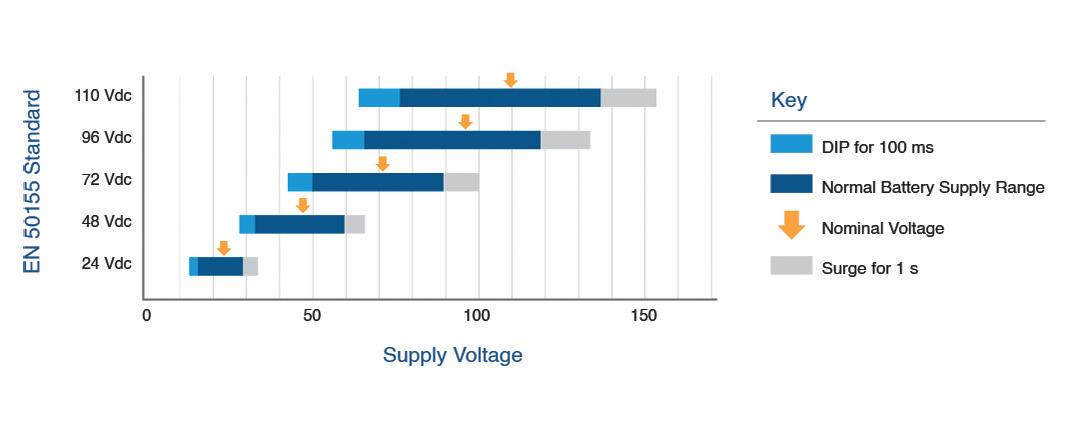

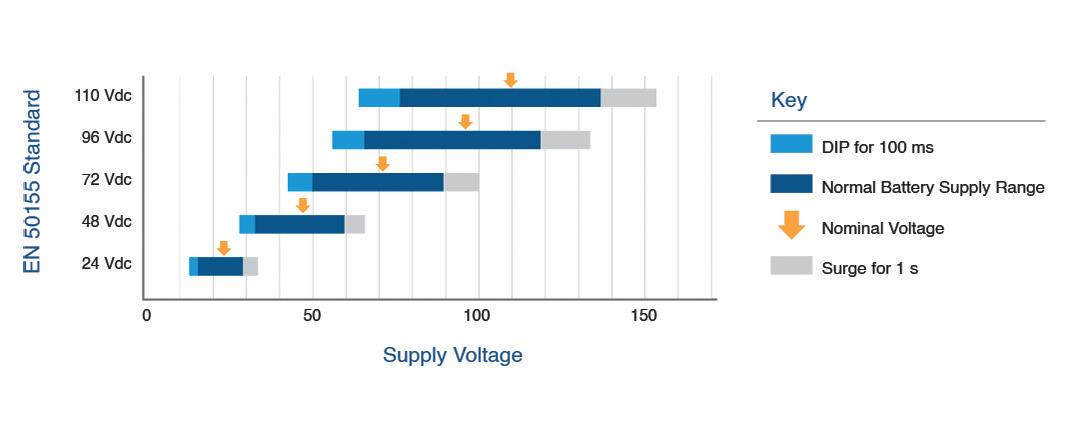

A case study helps illustrate the benefits of the approach. Consider as an example the power supply for a passenger information system as used on (light) rail vehicles. Light rail applications can experience long supply voltage interruptions. The EN 50155 standard for railway applications — rolling stock spells out requirements for the operation, design, and testing of electronic equipment on rail vehicles. Thanks to its comprehensive consideration of “harsh” environmental conditions, the EN 50155 is often considered for design of ruggedized industrial applications. This includes continued operation during an interruption of the supply voltage for a duration of up to 20 msec, a common occurrence in battery powered applications.

During the interruption, the input may be shorted. Power must come from an (external) hold-up capacitor bank. The design of the holdup circuit and the dimensioning of the capacitor bank are important parts of the overall application design process.

Light rail passenger information systems typically include a small screen, a field computer and networking peripherals such as industrial ethernet and/or IEEE 802.11 wireless communication. A 40-W power supply is typically adequate for handling these demands. Important electrical requirements of the dc supply include providing the industry standard 24, 48, 96, and 110-V battery system voltages as well as high and low input voltage limits, a maximum transient input voltage, and the maximum duration of an interruption the supply can handle.

We’ll consider three scenarios involving three different holdup circuits. Scenario A presents the use of a supply which also contains a dedicated holdup capacitor connection. Scenario B uses a comparable 12:1

Dr. André Buffing, L. Dinkelmann, Traco Power

Key requirements of the power circuit for a passenger information system on light (rail) vehicles.

Dimensioning and design of the capacitor bank used to ride through supply voltage interruptions.

26 DESIGN WORLD — EE NETWORK 2 • 2023 eeworldonline.com | designworldonline.com POWER

ELECTRONICS HANDBOOK