Capacitive Touch Input with the Raspberry Pi RP2040 Pico

Sponsored by Digi-Key and Raspberry Pi

In this class, we’ll explore how the Raspberry Pi RP2040 can detect touch inputs with the addition of a single resistor for each pin. We’ll explore the fundamentals of how capacitive touch works, and show how this can be done with the Pico using the CircuitPython programming language.

Watch the webinar at:

https://www.bigmarker.com/Embedded-Computing-Design/Capacitive-Touch-Input-With-the-Raspberry-Pi-RP2040-Pico

IOT DESIGN

Figure 2 | Pairing a microvisor architecture with Arm TrustZone-enabled devices allows complete development agnosticism and security. (Source: Twilio)

MORE WEBCASTS:

20 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

WATCH

https://www.embeddedcomputing.com/webcasts

The update service must be aware of the device’s current operational manifest, which defines what code/data should be stored in each defined memory area – either within on-die flash or in QSPI flash. Accordingly, when a new package is queued for FOTA, only areas that do not match would be deployed to the device.

A microvisor-based approach is no different, and the microvisor takes care of moving data required to apply an update from the cloud to a staging area in device QSPI storage, where it remains encrypted. Once the device has all the changed parts of the application stored safely in the staging area it applies the upgrade in a fail-safe and restartable way to ensure the upgrade appears atomic from the application’s point of view.

The application can be notified during the upgrade staging process, as it may want to indicate progress to an end user. Once the staging process is complete, the application is notified and can pick a convenient time to perform the upgrade. If required, the customer can force the upgrade to be applied at any time after staging, which may be used if the old code is behaving badly, for example.

How Can I Learn More About Microvisors?

If you’re interested in diving deeper into the microvisor architecture, consider reading the Twilio whitepaper “Architecture and Design Considerations for Modern IoT Infrastructure”, which is organized into two parts[5].

Part 1 addresses a broader audience, such as IoT product managers, project managers, and engineering managers. It lays out a typical device-side IoT architecture and describes the traditional implementation approach. It details the associated challenges and develops an argument for a different approach, now made possible through the hardware advancements described herein.

Part 2 addresses the experienced embedded engineer and explains Twilio’s thinking with regard to how the above-mentioned challenges can be effectively addressed with a new architecture.

Jonathan Williams is a product manager for IoT and wireless at Twilio. Having worked in both the semiconductor industry as well as in cloud video communications, he has a focus on building developer-friendly platforms that solve real-world problems. When not working on bringing IoT products to market, he can be found tinkering with his 1970’s rally car.

References:

1. Mattyhatton. (2022, January 17). Enterprise IOT Adopters Increasingly Favor Platform Companies and Offthe-Shelf Solutions. Transforma Insights. Retrieved February 8, 2023, from https://transformainsights.com/ blog/enterprise-iot-adopters-favour-platform-off-the-shelf

2. Dayaratna, A. (n.d.). Developing for the edge: Notes toward a definition of edge application development. IDC. Retrieved February 8, 2023, from https://www.idc.com/getdoc.jsp?containerId=US47198921

3. Microvisor and STM32U5, the Best Performance-per-Watt MCU, First to Support a New IoT Development Paradigm. ST life.augmented Blog. (2022, January 17). Retrieved February 8, 2023, from https://blog. st.com/stm32u5-microvisor/

4. What is Arm TrustZone Technology? Trustonic. (2021, April 16). Retrieved February 8, 2023, from https:// www.trustonic.com/technical-articles/what-is-trustzone

5. Twilio. (2022, May 27). Twilio Microvisor Architecture and Design Considerations for Modern IoT Infrastructure. Twilio. Retrieved February 8, 2023, from https://interactive.twilio.com/microvisor-modern-iotarchitecture

Open Specifications COM-HPC | COM Express | CompactPCI Serial IIoT | MicroTCA | ModBlox7 Empowering Embedded Computing Join Our Global Community and Experience the Value of Collaboration Visit us at embedded world Hall 3 Booth 3-544 www.picmg.org www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 21

Success Story: How RISC-V Is Enabling the Internet of Space

By Chad Cox, Production Editor

As objects exit Earth’s atmosphere, radiation levels become increasingly destructive to both organic and inorganic materials. The latter includes electronics, which are susceptible to Gamma rays, X-rays, and other high-energy particles that can cause single event upsets (SEUs, also known as bitflips) in memory, voltage spikes in analog circuitry, and other faults that can crash programs or entire systems.

Space radiation and its effects have been studied extensively over the past several decades. These efforts have resulted in the design and manufacture of radiationhardened (rad-hard) electronics that use special materials, exotic shielding techniques, and undergo exhaustive testing to withstand ionizing forces beyond Earth’s atmosphere for deployable periods of time.

Today, the TRISAT-R nanosatellite – a collaboration between the European Space Agency (ESA), Cobham Advanced Electronic Solutions (CAES), Skylabs, and the University of Maribor in Slovenia – continues that tradition (Figure 1). And it’s doing so on the strength of open-source RISC-V processor technology.

RISC-V is Out of this World

The TRISAT-R CubeSat is a scientific and educational mission led by the University of Maribor to map ionizing radiation in medium Earth orbit (MEO), a 6000 km-high band around Earth where various positioning, defunct radio, and future communications satellites reside. Roughly the size of a shoebox, the 3U, 10 cm x 10 cm x 30 cm satellite is built around the NANOhpm-obc onboard computer from Slovenian space technology company SkyLabs (Figure 2).

OPEN SOURCE EVERYWHERE

Designed into a 95 mm x 91 mm x 11 mm PC/104-compliant form factor, the

Figure 1 | The TRISAT-R is a research nanosatellite measuring the effects of ionizing radiation on commercial electronics in midearth orbit. (Source: SkyLabs)

22 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

NANOhpm-obc is built around Cobham Gaisler’s fault-tolerant 32-bit NOEL-V RISC-V processor IP core implemented alongside a single-precision floatingpoint unit in a Microchip PolarFire FPGA. The onboard computer integrates 2 GB of ECC-protected DDR3 memory and 2 GB of NVM flash in an EDAC-protected 1 GB redundant configuration for telemetry data, logs, and the like.

On top of that hardware, SkyLabs layered its NANOsky CMM Firmware

framework that provides the foundation for mission-specific applications and software functions.

To the knowledge of those involved in the project, when the NOEL-V processor onboard the NANOhpm-obc was launched into orbit on the ESA’s Vega-C rocket this summer, it marked the first time fault-tolerant RISC-V processor technology has been deployed in space.

The TRISAT-R is also outfitted with radiation detection instruments from SkyLabs, CERN, the European Council for Nuclear Research, and the European Space Agency (ESA) that measure the total ionization dose from high-energy particles as well as the effects of single ionizing events on electronics. These particles are analyzed locally on the nanosat using AI models, then radiation mitigation techniques are applied that show promise in extending the life of space bound COTS electronics. Communication between the nanosatellite’s various subsystems occurs over a redundant differential CAN bus for telemetry and telecommand (TMTC) data and LVDS for high-speed transfers.

The NANOhpm-obc’s 100 MIPS is leveraged for scintillation analysis of signals from an open GNSS receiver and to manage a software-defined radio (SDR) and 1.5 W VHF/ UHF transmitter that relay radiation effect data to ground control stations.

Radiation Hardening is RISC-y Business

“We are striking quite a lot of energetic particles and the solution here was to design solar panels that are able to operate at that radiation,” says Iztok Kramberger, PhD, leader of the TRISAT project and member of the Electrical Engineering and Computer Science (FERI) faculty at the University of Maribor. “We increased the thickness of the cover glass for the solar panels by adding a serum to the cover glass and we added specific conductive transparent material to guard against electrostatic discharges.”

The irony here is that while the TRISAT-R is measuring radiation, it’s also being destroyed by it. In MEO, the Earth’s magnetic field is 6x weaker than in low Earth orbits (LEO) just a few thousand km below. It’s also a frigid -19-26 ºC. And since there are no service calls to replace defective CubeSat components in space, the TRISAT-R’s onboard electronics must survive long enough on their own to make the program worthwhile.

The aerospace industry has historically met such requirements with rad-hard electronics proven to work every single time over many years. This has led to significant technology reuse – understandable given that a single chip like the PowerPC-based RAD750 from BAE Systems controlling the Perseverance Rover costs hundreds of thousands of dollars per unit.

But as use cases evolve, so do platform requirements, and the need for higher fidelity sensors, more sensitive instrumentation, and increasingly sophisticated algorithms has surpassed the abilities of 32-bit, 200 MHz processors like the RAD750. But just as important, if not more so for the reliability-centric aerospace industry, software support for RISC architectures with long spaceflight heritages like PowerPC and SPARC is quickly evaporating.

“We have been using SPARC very successfully for more than 20 years. LEON 1 and 2 processor development was started at the European Space Agency,” says Roland Weigand, a VLSI and ASIC engineer at the ESA. “Now SPARC is of course a very old, almost obsolete standard. We’re still using products based on SPARC, but we are aware that, long-term, the software support, the maintenance, the improvement of compilers will stop or has already stopped.

OPEN SOURCE EVERYWHERE

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 23

Figure 2 | SkyLabs NANOhpm-obc is the TRISAT-R’s onboard computer that equips a 32-bit Gaisler RISC-V processor for GNSS scintillation analysis and other tasks. (Source: SkyLabs)

“It’s been a couple years since the last commercial users, Fujitsu and Oracle, stopped supporting SPARC,” he adds.

These aren’t the only indicators that legacy technologies have run their course. For instance, features like delay slots built into SPARC processors that offset branch latency and allow one instruction to complete before a second enters the pipeline are now more of a programming nuisance than benefit. Similarly, register windows that facilitate “deep calling stacks in software is an obsolete feature,” Weigand explains.

Comparatively, Sandi Habinc, General Manager of Gaisler, believes that RISC-V offers “a simpler architecture” with “much more computing power per cycle.” The architectural optimizations of RISC-V mean that processors like the NOEL-V soft core can run at higher frequencies, which is critical in harsh environments like space because even if you use an advanced process node like 7 nm, so much radiation hardening is required around the processor core that it ends up being “10x slower than anything in the commercial world.”

“For us, every MHz we can bring to the table is important,” Habinc explains. “So definitely the simplicity of it is a huge advantage. The other one is of course implicitly built-in 16-bit support and the fact that we can now do microcontrollers and still use the same tools.”

“What did we do on the controllers with LEON? We had to invent our own compressions, reduce instruction set, which is not really a smart way to do it. It’s great if you’re Arm and you have 10,000 engineers, but for us that was a painful exercise to go through that,” Habinc continues. “On SPARC, we never went beyond 32 bits because that would change the whole software environment and too much effort because we need to maintain quite a lot of software.

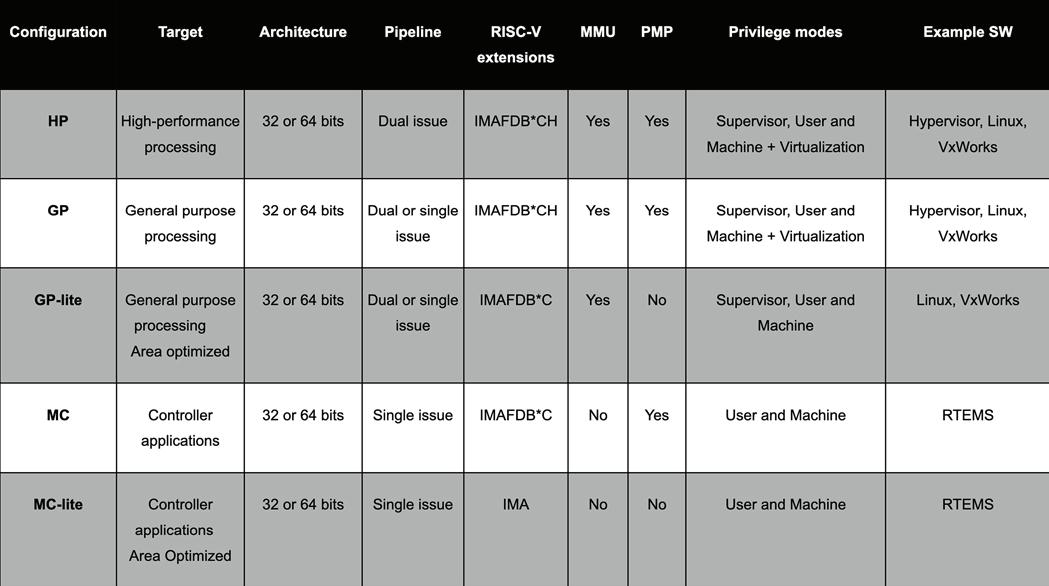

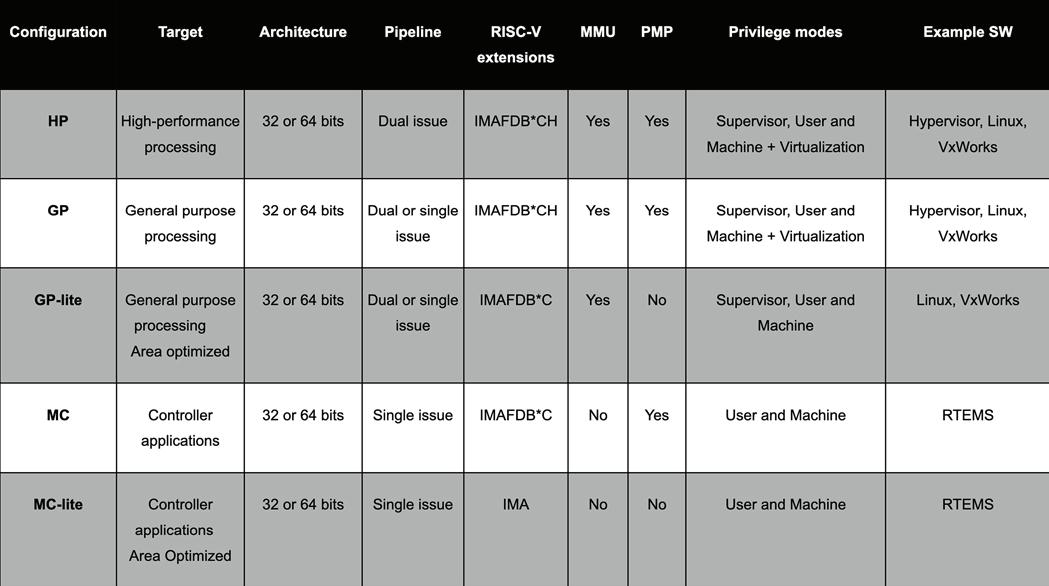

“With RISC-V, we can even scale down the cores we have today, reduce the number of pipeline stages, and really do a very thin single-stage, dual-stage microcontroller that we can fit everywhere,” the Gaisler GM goes on (Figure 3). “With RISC-V we can do the 32-bit microcontroller, we did a 64-bit version. Why not? It gives us the choice to target different uses in space.”

To ease the transition for aerospace engineering organizations, Habinc and his team are working on a multicore processor that integrates both SPARC and RISC-V cores.

“We qualify one chip but there’s basically a pin saying you want to boot SPARC or RISC-V, and this gives a tremendous advantage,” he adds.

The Internet of Space

Gaisler has already developed different variants of the NOEL-V processor, some of which include extensions like vector processing that will further accelerate workloads in space. For researchers like Kramberger, the increase in processing power onboard spacecraft reduces management overhead and creates new opportunities for studying the final frontier.

“One advantage is that the spacecraft can be more autonomous, which means that you don’t have to manage 600 or 700 satellites. You can’t have people do that. It has to be more or less autonomous,” he explains. “The second thing is that we are improving the data transfer between the satellite and the ground because you’re able to do more processing at the edge.

OPEN SOURCE EVERYWHERE

24 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

Figure 3 | Gaisler has developed multiple iterations of the NOEL-V RISC-V processor IP, in 32- or 64-bit flavors with dual- or single-issue pipelines that support various RISC-V instruction set extensions. (Source: CAES)

“Then of course you can reduce the data downstream towards the Earth,” he continues. “So, for example, a typical remote sensing application still today, there is a camera recording, and this data is transferred to the Earth and on Earth we do things with the data. The resolution requires higher and higher data downlink bandwidth. But doing AI at the edge provides capabilities to take the interesting data within the orbit and transfer only the results, meaning much lower requirements on bandwidth.

“That is quite similar to the Internet of Things on Earth,” Kramberger progresses. “We could call it the ‘Internet of Space Assets’ that gives us the ability to do more sensing of our environment, which is not only the planet but the Solar System as such.”

For now, the TRISAT-R nanosatellite is fully operational in an elliptical orbit, “drifting between 18 and 23 degrees,” says Dejan Gačnik, CTO of SkyLabs. “All essential equipment has been commissioned … all parameters are nominal.”

Unfortunately for the TRISAT-R, the end is already near. Space radiation will eventually take its toll on the tiny satellite at which point it will have to be decommissioned. But given that its primary mission is to measure and analyze the effects of ionizing radiation on spacecraft electronics, Gačnik believes the mission will be a success if TRISAT-R can endure for at least six months. It has already been in orbit for almost four.

But for RISC-V, the TRISAT-R is just the beginning. Gaisler and the ESA continue to develop new generations of space processors based on the technology. Microchip, who has RISC-V technology deployed on the International Space Station, continues to advance it’s PolarFire FPGA portfolio with radiation-tolerant versions that include a SiFive soft CPU core for running user applications.

For organizations like ESA and NASA, RISC-V is the obvious choice as they continue to build space exploration programs on open, high-performance, and flexible commercial electronics.

“Going from one open standard to another open standard like RISC-V is the most logical choice,” Weigand says. “It’s simply an advance of technology, which helps improve the performance and the software development flow.”

“For us, it’s a logical step forward.”

Editor’s note: “RISC-V in Space” workshops were held at the 2022 RISC-V Summit and

Media partners Get your free ticket now! embedded-world.com/voucher Use the voucher code GG4ew23 JOIN THE EMBEDDED COMMUNITY 14–16.3.2023 EW-23_Ad_Visitors_185x130mm_EN_3mm.indd 1 30.11.22 08:32

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 25

The 2023 Embedded Computing Design embedded world issue showcases embedded tools and solutions for those designing in the areas of industrial control, edge computing, autonomous machines, and more.

Development & Evaluation Kits

All-in-one, super-portable, multi-protocol Type-C analyzer with voltage tracking, integrated logic analysis, and Alternate Mode support.

Pocket-sized and bus-powered, the Ellisys Type-C Tracker delivers comprehensive support for a multitude of protocols and electrical signaling that operate over the USB Type-C connection standard.

Detailed decoding of packets, transactions, and other communications is provided in a flexible and easy to understand manner over the field proven and ubiquitous Ellisys software application. The Tracker provides a variety of error detections, precision timing tools, and performance measurement tools.

Designed with ease-of-use in mind, the Type-C Tracker is the ideal companion for a wide variety of tasks associated with Type-C product development.

FEATURES

Ą All-in-One: Precisely synchronized and concurrent capture of USB Power Delivery protocol (including ALT modes), Type-C voltages, USB 2.0 protocol and classes, Thunderbolt™ 3 and USB 4 sideband, I2C, Type-C Port Controller Interface, UART, GPIO/Logic, SWD, SPI, and DisplayPort™ auxiliary (AUX) signaling.

Ą Bus-Powered: Just attach to your computer’s USB port and go, no bricks to carry around.

Ą Super Portability: Pocket-sized at 63.5 x 63.5 x 12 mm (2.5" x 2.5" x 0.47")

Ą Real-Time Display: Visualize captured traffic in real time with the efficiency of 5th generation Ellisys protocol analysis software

Ą Professional Software: Use the acclaimed, widely adopted and highly flexible Ellisys multi-protocol analysis software.

https://ellisys.com/products/ctr1

2023 EMBEDDED

DEVELOPMENT & EVALUATION KITS Ellisys 26 EDGE AI & MACHINE LEARNING Vecow 27 EMBEDDED HARDWARE Synaptics 28 congatec 29-30 Real-Time Systems 30 embeddedTS 31-32 iBASE Technology Inc. 32 Lattice Semiconductor Corporation 33 Mactron Group 34 Sealevel Systems, Inc. 34 EMBEDDED PROCESSING SECO USA 35 INDUSTRIAL AUTOMATION & CONTROL PEAK-System Technik GmbH 36-38 IOT Synaptics 39 WIRELESS Ellisys 38 Embedded Computing Design

WORLD

Ellisys www.ellisys.com sales.usa@ellisys.com 866-724-9185 @Ellisys1 www.linkedin.com/company/ellisys

Ellisys Type-C® Tracker™

26 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

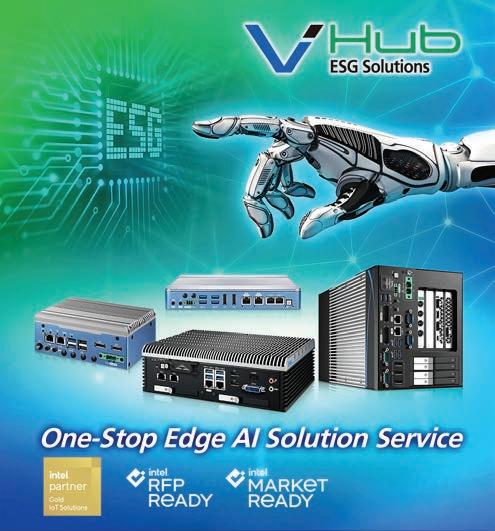

One-Stop Edge AI Solution Services

Vecow is a team of global embedded experts. We commit to designing, developing, producing, and selling industrial-grade computer products. All of our products are leading in performance, trusted in reliability, exhibit advanced technology and innovative concepts. Vecow offers One-Stop Edge AI Solution Services, AI Inference Systems, High-performance Fanless Systems, In-Vehicle Computing Systems, Expandable Computing Systems, Ultra-compact Fanless Systems, Single Board Computers (SBC), Industrial Motherboards, Multi-Touch Computers & Displays, Ethernet Switches, Frame Grabbers, Embedded Peripherals and Design & Manufacturing Services with leading performance, trusted reliability, advanced technology, and innovative concepts.

Vecow aims to be your trusted embedded business partner. Our experienced service team is dedicated to creating and maintaining strong partnerships and one-stop integrated solutions. Our services are specific and consider each partner’s unique needs in regards to: Machine Vision, Autonomous Vehicles, Robotic Control, Digital Rail, Public Security, Transportation & V2X, Smart Factory, and any Edge AI applications.

FEATURES

VHub ESG Solutions: Smart Digital Factory Accelerator

Vecow VHub ESG is an one-stop AIoT solution service to accelerate digitalization and management tasks in the factory. Vecow delivers both hardware and software integrated turnkey solutions to facilitate the requirements of Sustainable Development Goals (SDGs), including Carbon Intensity, Facility Management, Optimized Productivity, and Workforce Management.

https://reurl.cc/zraxzN

ECX-3000: Workstation-grade Fanless System

The latest 13th Gen Intel® Core™ i9/i7/i5/i3 Processor with Intel® 600 Series chipset, supports max 24 cores and 32 threads with advanced performance hybrid architecture; Max 8 2.5GigE LAN w/4 IEEE 802.3at PoE+, dual 10GigE LAN, 6 USB 3.2 Gen 2, DC 9V to 50V, Software Ignition Control; Intel® vPro, TCC, TSN, TPM 2.0; Optional VHub AIoT Solution Service accelerates Edge AI applications.

https://reurl.cc/7j85yd

https://reurl.cc/VRbWdQ

ECX-3000 PEG: Workstation-grade AI Inference System

The latest 24-core 13th Gen Intel® Core™ i9/i7/i5/i3 Processor with Intel® 600 Series chipset, up to 65W TDP CPU; Supports outstanding AI computing productivity by independent NVIDIA®/ AMD graphics cards or AI accelerate cards, up to 200W power budget; 6 GigE LAN w/4 IEEE 802.3at PoE+, DC 12V to 50V, Software Ignition Control; Intel® vPro, TCC, TSN, TPM 2.0; Optional VHub Solution Service accelerates Edge AI applications.

https://reurl.cc/4XzZ33

EAC-5000: Expandable Edge AI Computing System

Advanced NVIDIA® Jetson AGX Orin™ Platform supports up to 275 TOPS AI performance; the latest NVIDIA® Ampere™ architecture, max 2048 NVIDIA® CUDA® cores and 64 Tensor cores; 2 GigE LAN, 5 USB, 2 Isolated CAN FD, 8 Fakra-Z for GMSL 2/1 automotive cameras, PCIe 4.0 x8 supports optional multiple 10GigE/PoE LAN/USB, multiple 5G/4G/LTE/WiFi/BT/GPS, DC 9V to 50V, Fanless -20°C to 70°C operation.

https://reurl.cc/4XzZ43

Embedded Computing Design

www.vecow.com sales@vecow.com +886 2 22685658 @VecowCo www.linkedin.com/company/vecow-co.-ltd Edge AI & Machine Learning

Vecow

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 27

Synaptics Resonate™ Revolutionizes Audio and Haptic Feedback for Embedded Displays

Synaptics Resonate is a game-changing solution that adds audio and haptic feedback to the rear of embedded displays, directing audio outward, directly from the glass surface. The innovative design saves space, lowers cost, and reduces power consumption, while also improving system reliability by enabling water and dust ingress prevention. Combined with high-quality audio and a more immersive viewing and interactive experience, the technology has applications ranging from industrial, automotive, and manufacturing, to portable media players, consumer electronics, toys, and gaming platforms.

Resonate uses piezoelectric transducers attached to the back of the display panel. These are driven by a Synaptics proprietary amplifier such that they vibrate the display glass to produce the required audio waves and haptic feedback. With direct line of sight from the sound source to the user, the result is a more immersive viewing experience. The removal of traditional speakers and associated vents means the product casing can be fully sealed, enabling dust and waterproof designs, making Resonate ideal for challenging embedded environments.

Other features include high sound pressure levels (SPLs), an efficiency improvement of up to 80%, fewer components for lower BOM, a smaller footprint, higher reliability, less weight – particularly with the removal of linear resonant actuators (LRAs) for haptics – and the opportunity for a more elegant industrial design that is protected from environmental hazards.

Haptic feedback is also enhanced, as it correlates directly with the displayed content. This capability is particularly important in emergency situations where both haptic and audio alerts can be used. In consumer applications, such as gaming, the user can see, hear, and now feel exactly what’s happening on the display in real-time.

The nature of piezoelectric transducers is such that the reverse is also true: users can apply pressure to the screen, causing the piezoelectric transducers to produce a corresponding electrical signal that can be detected by the system to, for example, control acceleration. This adds a third axis (z) of user control.

Resonate is available now.

To find out more, go to www.synaptics.com/resonate.

FEATURES

Ą Embeds audio and haptic feedback with displays

Ą Up to 80% improvement in energy efficiency

Ą Enables dust and waterproof displays with audio

Ą Lower cost, smaller footprint

Ą Immersive user experience: direct line of sight from audio source to ears

Ą Adds third axis (z) of user control to displays with force sensing

Ą High-quality audio

Ą High sound pressure levels

Embedded Computing Design

Embedded Hardware www.synaptics.com/resonate Synaptics Incorporated www.synaptics.com sales@synaptics.com www.synaptics.com/contact www.linkedin.com/company/synaptics @ SynaCorp

28 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

Micro-ATX carrier board eco-system for COM-HPC

The new conga-HPC/uATX industrial-grade COM-HPC carrier board in Micro-ATX form factor is designed for embedded longterm availability of at least seven years, which eliminates the design risks, revision requirements and supply chain uncertainties of standard or semi-industrial-grade motherboards that are usually only deliverable for three to five years. As it is processor socket and vendor independent, the board can be equipped with any high-end Computer-on-Module available in COM-HPC Client Size A, B or C, making OEM designs even more flexible and sustainable. Impressive scalability across the entire range of 12th Generation Intel Core processor-based COM-HPC modules. Performance options for the new conga-HPC/uATX carrier board range from the conga-HPC/cALS COM-HPC Client Size C modules, offering the currently highest embedded client performance with 16-core Intel Core i9 processor, to the masters of price/ performance optimization – the conga-HPC/cALP COM-HPC

Client Size A modules with Intel Celeron 7305E processor.

The combination of application-ready industrial-grade COMs & carrier boards with tailored cooling solutions and comprehensive BSPs for all leading RTOSes and the real-time hypervisor from Real-Time Systems is perfect for fastest time-to-market, produces lowest non-recurring engineering costs, enables customers to react very quickly to changing market requirements and reduces the effort to scale the performance of Micro-ATX based systems to a minimum. It allows customers to create a full product portfolio based on one single carrier concept.

The carrier board offers the latest interface enhancements such as PCIe Gen4 and USB 4 and is a perfect fit for system designs with congatec’s latest high-end COM-HPC Client modules based on the 12th generation Intel Core i9/7/5/3 desktop processors (formerly code-named Alder Lake-S). Most impressive is the fact that engineers can now leverage Intel’s innovative performance hybrid architecture. Offering of up to 16 cores/24 threads, 12th Gen Intel Core processors provide a quantum leap in multitasking and scalability levels.

Next-gen IoT and edge applications benefit from up to 8 optimized Performance-cores (P-cores) plus up to 8 low power Efficient-cores (E-cores) and DDR5 memory support to accelerate multithreaded applications and execute background tasks more

efficiently. Optimized for highest embedded client performance, the graphics of the LGA processor based modules delivers now up to 94% faster performance and its image classification inference performance has nearly tripled with up to 181% higher throughput. In addition, the modules offer massive bandwidth to connect discrete GPUs for maximum graphics and GPGPU based AI performance.

FEATURES

Ą Application Carrier Board for COM-HPC Client Type Modules (Sizes A, B, C) in Micro-ATX form factor. Size 244 x 244 mm2

Ą Besides highest bandwidth and performance, the new flagship COM-HPC Client modules impress with dedicated AI engines supporting Windows ML, Intel Distribution of OpenVINO toolkit and Chrome Cross ML

Ą Different AI workloads can seamlessly be delegated to the P-cores, E-cores, as well as the GPU execution units to process even the most intensive edge AI workloads

Ą The built-in Intel Deep Learning boost technology leverages different cores via Vector Neural Network Instructions (VNNI), and the integrated graphics supports AI accelerated DP4a GPU instructions that can even be scaled to dedicated GPUs

Ą Intel’s lowest power built-in AI accelerator, the Intel Gaussian & Neural Accelerator 3.0 (Intel GNA 3.0), enables dynamic noise suppression and speech recognition and can even run while the processor is in low power states for wake-up voice commands.

Embedded Computing Design

Embedded Hardware www.congatec.com congatec www.congatec.com sales-us@congatec.com 858-457-2600 www.linkedin.com/company/congatec/ @ congatecAG

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 29

congatec i.MX 8M Plus Starter Set

congatec extends its i.MX 8 ecosystem with a new starter set for AI accelerated intelligent embedded vision applications. Based on a SMARC Computer-onModule with i.MX 8M Plus processor, the starter set’s sweet spot is the utilization of the new processor integrated NXP Neural Processing Unit (NPU). Delivering up to 2.3 TOPS of performance for deep learning based artificial intelligence, it can run inference engines and libraries such as Arm Neural Network (NN) and TensorFlow Lite. It also integrates seamlessly with Basler embedded vision software to give OEMs an application ready solution platform for the development of nextgeneration AI accelerated embedded vision systems.

Typical applications are wide ranging, from price sensitive automated checkout terminals in retail to building safety, and from in-vehicle vision for navigation to surveillance systems in busses. Industrial use cases include HMIs with vision based user identification and gesture based machine operation as well as vision supported robotics and industrial quality inspection systems.

FEATURES

Ą 4 powerful Arm Cortex®-A53 cores, 1x Arm Cortex®-M72 controller and the NXP NPU to accelerate deep learning algorithms at the edge and comes with passive cooling.

Ą 3.5 inch carrier board conga-SMC1/SMARC-ARM directly connects the 13 MP Basler dart daA420030mci BCON for MIPI camera with an F1.8 f4mm lens via MIPI CSI-2.0 without any additional converter modules. Next to MIPI CSI-2.0, USB and GigE vision cameras are also supported.

Ą On the software side, congatec provides a bootable SD card with preconfigured boot loader, Yocto OS image, matching BSPs, and processor-optimized Basler embedded vision software enabling immediate AI inference training on the basis of captured images and video sequences.

The Real-Time Systems Hypervisor splits the hardware into individual partitions containing one or more processor cores, some memory and PCI devices. Different partitions may run different operating systems or multiple instances of the same OS. Two different OS Execution Modes that may run on different processor cores in parallel:

• With the Privileged Mode you have direct hardware access, therefore, no added latencies and additional (latency-free and hardware-assisted) protection, which is configurable like Virtual MMU, restricted I/O, IOMMU.

• With the Virtualized Mode you have pass-through access to assigned devices, you can run unmodified operating systems and update them at any time, or processor cores running GPOS’s like Windows or standard Linux distributions.

The RTS Hypervisor sits in-between the hardware and the OS to ensure proper isolation. You have complete isolation of OS in memory, no inter-dependence, reboot of any system is possible at any time and it is definable in the boot sequence.

FEATURES

Ą Configuration of RTS Hypervisor is performed through a simple text file

Ą Works out-of-the-box without customization

Ą Runs on any PC from low-power modules to multi-socket servers

Ą Secure design with no unessential interfaces or backdoors

Ą Rapid inter-system communication and synchronization

Ą All popular OS supported

Embedded Computing Design

Embedded Hardware Real-Time Systems GmbH www.real-time-systems.com/ info@real-time-systems.com +49 (0) 751 359 558 – 0 www.linkedin.com/company/real-time-systems-gmbh +1 425-802-0240

REAL-TIME Hypervisor

Embedded Hardware

congatec www.congatec.us sales-us@congatec.com 858-457-2600 www.linkedin.com/company/congatec twitter.com/congatecAG 30 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

TS-4900

The TS-4900 is a high-performance TS-SOCKET System on Module based on the NXP i.MX6 CPU, which implements the Arm® Cortex®-A9 architecture clocked at 1 GHz (Single or Quad Core) and paired with 1GB or 2GB of DDR3 RAM.

Several industry-standard interfaces and connections such as Gigabit Ethernet, WiFi and Bluetooth, USB, SATA II, PCI Express, and more make the TS-4900 a great fit for nearly any embedded systems application, especially those needing wireless connections like industrial internet of things gateway.

FEATURES

Ą 1 GHz Single or Quad Core Cortex-A9 Arm CPU

Ą Up to 2 GB DDR3 RAM

Ą 4GB MLC eMMC flash storage

Ą Bluetooth and WiFi onboard radios

Ą Up to 70x DIO, 2x I2C, 1x I2S, 2x SPI, 2x CAN

Ą Industrial temperature range (-40°C to 85°C)

Embedded

TS-7100-Z

Time and again at customer visits, embeddedTS heard the same thing, “We love your single board computers, but make them smaller! They have to go inside this cabinet, and we need room for everything!” We listened. embeddedTS is proud to introduce the TS-7100-Z, our smallest single board computer in an optional DIN-mountable enclosure that measures 2.4" by 3.6" by 1.7", powered by the Arm® Cortex®-A7 based iMX6 UltraLite CPU. It ships with industry-standard interfaces, including Ethernet, USB, RS-232, RS-485, and CAN. For wireless connectivity, the TS-7100-Z comes with WiFi and Bluetooth module, as well as a NimbeLink/Digi cellular modem and mesh network socket.

With all of these features packed into a smaller footprint, not only will the TS-7100-Z fit in your cabinet, but it can also help to replace other peripherals and modules to free up even more space and get more done. Combining all of these components into one small DIN mounted unit, we provide the ability to promote hot swapping in the field, limiting costly technician time and troubleshooting.

FEATURES

Ą NXP i.MX 6UltraLite 696 MHz Arm® Cortex®-A7 based SPC with FPU

Ą 4 GB eMMC Flash Storage

Ą 2 KB FRAM Storage

Ą 512 MB RAM

Ą 2x 10/100 Ethernet Ports, 2x USB Host Ports, 2x Serial Ports, RS-485 Ports, CAN Port

Ą Industrial Temperature Range (-40 °C to 85 °C)

embeddedTS www.embeddedts.com sales@embeddedts.com 480-837-5200 @ts_embedded https://www.embeddedts.com/products/ts-4900 Embedded Hardware www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 31

Embedded Computing Design

embeddedTS

www.embeddedts.com sales@embeddedts.com 480-837-5200 @ts_embedded

https://www.embeddedts.com/products/ts-7100-z Hardware

A wide variety of software platforms are available, including Linux, Ubuntu Core, Android, and QNX for flexibility in matching your embedded system requirements.

Powered by the Marvell Armada 385 Dual Core 1.3 GHz Arm® Cortex®-A9based CPU, the TS-7800-V2 industrial Single Board Computer (SBC) stands out from the crowd with its high-performance components, connectivity options, and an unbelievable feature set packaged into a small footprint in both size and power. It's a general-purpose, low-power SBC ready to tackle demanding applications, including data acquisition, IoT, industrial automation, and anything in between.

Each component on the TS-7800-V2 has been carefully chosen to ensure reliable operation in the field. Data is reliably stored in the onboard eMMC flash. With the included heat sink, the fanless design of the TS-7800-V2 is able to withstand high vibration, and even with two CPU cores running at 1GHz and tasked to their max the system can operate at a wide temperature range of -40 °C to 85 °C.

FEATURES

Ą Marvell Armada 385 Dual Core 1.3 GHz Arm-based CPU

Ą 1 DDR3 RAM

Ą 4 GB MLC eMMC Flash

Ą 20k LUT Cyclone FPGA (145 Various I/O Pins)

Ą 5x RS-232, 4x TTL UART, 2x RS-485 and CAN Bus

Ą 6x PWM Channels

MBB-1000

The MBB-1000 is a 13th/12th Gen Intel® Core™ processors (formerly Alder Lake) powered ATX motherboard. It is built with long-term reliability for graphics-intensive applications such as AIoT, digital signage, medical imaging, video surveillance and interactive kiosks.

The MBB-1000 supports four 4K independent displays with 1x HDMI (2.0b), 1x DVI-D, and 2x DisplayPort 1.4a (DP++). It features 5G/4G/LTE connectivity with a 5G-compatible M.2 B3052 socket and discrete WiFi 6E with the new frequency band ranging from 5.925 to 7.125 GHz. The board comes with four high-speed DDR4-3200 RAM sockets with a total capacity of 128GB and extensive I/O interfaces with 2x Intel® 2.5G LAN, 10x USB ports, 4x SATA III, 4x serial ports, and multiple expansion slots including 1x PCI-E(x16), 2x PCI-E(x4), 1x PCI-E(x1), 2x PCI, and 4x M.2 slots.

The industrial platform will be available with three different Intel chipsets (R680E/Q670E/W680) and Win10 (64-bit), Linux Ubuntu (64-bit), and Windows Server 2022 OS support. For more details, please visit www.ibase.com.tw.

FEATURES

Ą 13th/12th Gen Intel® Core™ i9/i7/i5/i3 / Pentium® / Celeron® processors

Ą 4x DDR4 DIMM, Max.128GB

Ą Intel® processor integrated graphics supports HDMI (2.0b), DVI-D, and DisplayPort (1.4) (DP++)

Ą Dual Intel® 2.5G LAN

Ą 8x USB 3.1, 2x USB 2.0, 4x SATA 3.0, 4x COM, 4x M.2 (B-Key, E-Key/ 2x M-Key)

Ą 1x PCI-E(x16) (Gen5.0), 2x PCI-E(x4) (Gen4.0), 1x PCI-E(x1) (Gen3.0), 2x PCI

Ą Watchdog timer, Digital I/O, iAMT (16.0), TPM (2.0)

https://www.ibase.com.tw/en/product/category/Embedded_Computing/Motherboard/ATX_Motherboard/MBB-1000

Embedded Computing Design

IBASE Technology Inc ibase.com.tw sales@ibase.com.tw +886-2-26557588 @iBaseTech www.linkedin.com/company/ibase-technology-inc-/

Embedded Hardware

embeddedTS www.embeddedts.com sales@embeddedts.com 480-837-5200 @ts_embedded https://www.embeddedts.com/products/TS-7800-V2

Hardware 32 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

TS-7800-V2

Embedded

Companies today are challenged by a fast-evolving technology landscape, a seemingly insatiable hunger for more connectedness and intelligence, and an explosion of data generated at the Edge. Moreso than ever before, system designers and developers need efficient and flexible processing solutions that can keep pace with this accelerated demand for innovation.

These customer needs are what inspired Lattice Semiconductor to create the Lattice Avant™ platform, extending the company’s low power leadership to span the small and mid-size density FPGA portions of the market.

Advancing FPGA Innovation

Architected from the ground up, Lattice Avant will enable designers with the power efficiency, performance, and small size leadership they know and expect from Lattice, with advanced connectivity and optimized compute capabilities at higher capacities than previous Lattice devices. This enables Lattice to address a broader set of customer applications than ever before.

A Closer Look at Lattice Avant

The Lattice Avant platform is designed at every level to deliver power efficiency, advanced connectivity, and optimized compute capabilities not previously available in mid-range FPGAs. While there is a lot of innovation worked into the platform, key architectural highlights include 25G SERDES and parallel I/O standards that address a wide variety of interface, and external memory interface support including DDR4, DDR5, and LPDDR4 along with legacy standards.

Addressing Key Customer Needs

Lattice Avant was born out of customer demand for compelling mid-range FPGA solutions for Communications, Computing, Industrial, and Automotive applications. When discussing their needs, it became clear that they were increasingly concerned with three key things: power efficiency, performance, and form factor – which aligned perfectly with what Lattice does best. As compared to existing FPGAs serving the mid-range FPGA segment, Lattice Avant features:

• Market-leading power efficiency with up to 2.5X lower power helping system and application engineers achieve power and thermal design efficiencies, improve operating costs, and enhance reliability

• Best-in-class performance delivering up to 2X faster throughput providing increased bandwidth and enabling reduced number of SERDES links, system cost and size.

• Industry leading form factor offering up to 6X smaller package sizes to enable size efficient system designs

Lattice Avant will leverage existing Lattice software solutions and application-specific solution stacks they already know and understand. This familiarity will help reduce adoption time and accelerate development.

The Lattice Avant platform is architected for scalability that will enable the rapid development of multiple new device families, available today with the Lattice Avant™-E FPGA family. Lattice Avant-E FPGAs are designed to solve key customer challenges at the Edge by combining class-leading power efficiency, size and performance with an optimized feature set tailored to the needs of Edge applications like data processing and AI.

To learn more about the Lattice Avant platform, visit the platform page: www.latticesemi.com/AvantPlatform

FEATURES

Ą High bandwidth SERDES

Ą Low power FPGA fabric

Ą External memory support

Ą Best-in-class security

Ą Fast and flexible programmable I/O

Ą Small form factor

Embedded Computing Design

Embedded Hardware www.latticesemi com/AvantPlatform Lattice Semiconductor www.latticesemi.com 503-268-8000 @ latticesemi www.linkedin.com/company/lattice-semiconductor/

Lattice Avant™ FPGA Platform

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 33

6 Various Applications of 21.5" Touch Panel PC

MACTRON GROUP – MTG from Taiwan targets Touch Embedded Systems as the goal. Its business concept – “TRANSFORMER” means to approach various markets through the diversity of its hardware abilities. At Embedded World, you will visit their 6 types of main 21.5 inches Touch Panel PCs for the global markets among Medical, Automation, and Commercial. And they will release more new products than those. Its popular Aluminum Die-Casting Touch Panel PCs – WCP and WMP series will further be equipped with the powerful 12th Gen Intel Core i series with the Iris GPU. To achieve Touch Science furtherly, they are also on the road of AIoT and Big Data to achieve convenience and intuition in people’s daily lives. Besides pioneering the markets, expanding the testing and assembling plant in 2023 is what they're planning as well to maximize the buffer capacity. Go check their booth out for more information.

sales@mactrongroup.com

www.mactrongroup.com

HazPAC® 10 Rugged Panel PC

The HazPAC® 10 Rugged Panel PC is certified by ATEX, IECEx, and for Class I, Division 2 (Groups A, B, C, D, T4). Designed for Windows 10® IoT Embedded, the HazPAC 10 system delivers powerful Intel® processing combined with a bright, LCD, five-wire resistive touchscreen. The fanless industrial computer features a wide -40°C to 60°C operating temperature making it perfect for a wide variety of embedded and HMI applications. The touchscreen integrates a glass surface that is waterproof, and impervious to flames, chemicals, solvents, and stylus use for maximum abrasion and scratch resistance. The HazPAC 10’s aluminum front bezel maintains NEMA 4/IP64 protection from sprayed liquids including rain, snow, splashes, hose downs and other pressurized water streams. For further protection, the bezel is sealed against dust and dirt. With its Class I, Division 2 rating, the HazPAC 10 is also approved for locations where flammable liquids or gases are handled and processed. Powered by an Intel® Atom® E3845 quad-core processor, the system has 8GB of DDR3 RAM and a 64GB CFast SSD port for maximum performance in embedded systems. Standard I/O includes Ethernet, serial, USB and digital interfaces, as well as an mPCIe expansion slot.

FEATURES

Ą WMP – Medical Premium

Ą WCP – Commercial Premium

Ą WAM – Panel Mount

Ą WAP – Waterproof Design

Ą WCA – Commercial Android

Ą WCS – Commercial Windows

+8862 2795 1668

@MactronGroup

Embedded

FEATURES

Ą Available in 8.4" or 15" touchscreen models

Ą Certified by ATEX, IECEx, and for Class I, Division 2 (Groups A, B, C, D, T4)

Ą Durable five-wire resistive touchscreen

Ą Future-proof COM Express design

Ą Ethernet, serial, USB, and digital interfaces

Ą mPCIe expansion slot

Ą Wide -40°C to 60°C operating temperature range

Embedded Computing Design

Sealevel Systems, Inc. www.sealevel.com sales@sealevel.com 864-843-4343 @SealevelSystems www.linkedin.com/company/sealevel-systems-inc/

https://www.sealevel.com/product/h1400811-hazpac-10-rugged-panel-pc-touchscreen/ Hardware

MACTRON GROUP CO., LTD.

Embedded Hardware 34 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

www.linkedin.com/company/13437871/admin/

SECO Electronics Technology: From Edge to AI

Leveraging decades of expertise in turnkey embedded computing design, manufacturing, and Internet of Things (IoT) and Artificial Intelligence (AI) solutions, SECO enables businesses with smart solutions that accelerate digital transformation.

Edge Computing

SECO edge platforms feature state-of-the-art processing technologies, based on x86, Arm®, and FPGA architectures. Products are available as computer-on-module (COM) and single board computer (SBC) embedded boards, mountable human-machine interface (HMI) assemblies, and fully packaged devices – off-the-shelf or customized.

SECO HMI panel PCs are available with various processor, installation, and display size options from 5.0” to 21.5”. The TANARO 7.0 series, featuring NXP’s i.MX 8M Mini processor, is designed for rear or panel mounting.

Off-the-shelf COM and SBC products feature leading processing technologies (NXP, Intel®, AMD) compliant with major standards (SMARC, QSeven®, COM-HPC®, COM Express®, Pico-ITX, eNuc) or application-optimized. Latest SECO solutions include: COM-HPC®

Client ORION with 12th Gen Intel® Core™ processors (for automation, sensor fusion, and AI at-the-edge); COM Express® CALLISTO with 13th Gen Intel® Core™ processors (for AI and IoT end devices); SMARC FINLAY with Intel® Atom® processors x7000E Series or Intel® Core™ i3 processors (for power-efficient deep learning inference and UHD media processing); Arm®-based SMARC MAURY with NXP i.MX93 (for low-power, headless, or simple display handheld devices) and SMARC WILK with MediaTek Genio 7000 (for AI-accelerated and rich graphics applications); Qseven® ATLAS and PicoITX ICARUS with Intel® Atom™ x6000E Series (for AIoT applications).

System integration-ready boxed fanless embedded computers, communication gateways, and payment systems complete SECO’s off-the-shelf edge platforms. SECO offers custom design and integration of electronic devices, built for reliability and robustness.

Intelligent Platform Solutions

SECO makes the implementation of IoT infrastructure and business-enhancing AI applications easy with CLEA, an edge and cloud AI-IoT platform. With instances running on edge devices managed by a cloud-based software hub, CLEA can be deployed with minimal configuration, while also easily expandable. CLEA facilitates real time device monitoring, analytics, infrastructure management, predictive maintenance, secure remote software updates, and more. The platform enhances intelligence, with easy aggregation and visualization of data from multiple sources for intuitive big-picture analysis and optimization.

FEATURES

Ą Off-the-shelf embedded products: COM, SBC, mountable HMI devices, and payment systems compliant with widely used standards that reduce time-to-market.

Ą Operating systems for edge devices: Linux, Android, Windows, RTOS.

Ą Customized computing platforms: custom-designed circuitry, software, and devices that meet unique product requirements.

Ą CLEA edge and cloud AI-IoT platform: software solution that easily deploys intelligence where devices and data become actionable value.

Ą Embedded AI: algorithms that autonomously analyze and optimize operation on the edge device.

Ą Product development: design and production of rugged high reliability electronic devices, including rugged tablets, devices, and industrial equipment.

Ą World-class electronics manufacturing: ISO 9001 and 13485 certified.

Embedded Computing Design

SECO www.seco.com +1-240-558-2014 sales.us@seco.com www.linkedin.com/company/seco-spa/ Embedded Processing www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 35

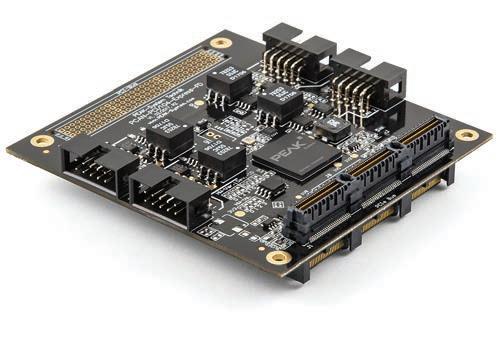

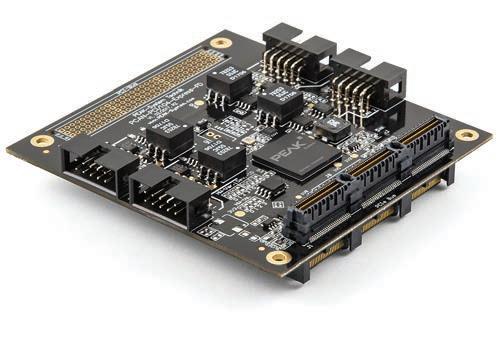

FEATURES:

Ą Form factor PC/104

Ą Multiple PC/104 cards can be operated in parallel (interrupt sharing)

Ą 14 port and 8 interrupt addresses are available for configuration using jumpers

Ą 1 or 2 High-speed CAN channels (ISO 11898-2)

Ą Bit rates from 5 kbit/s up to 1 Mbit/s

Ą Compliant with CAN specifications 2.0A (11-bit ID) and 2.0B (29-bit ID)

Ą Connection to CAN bus through D-Sub slot bracket, 9-pin (in accordance with CiA® 303-1)

Ą NXP SJA1000 CAN controller, 16 MHz clock frequency

Ą NXP PCA82C251 CAN transceiver

Ą 5 V supply to the CAN connection can be connected through a solder jumper, e.g., for external bus converter

Ą Optionally available with galvanic isolation on the CAN connection up to 500 V, separate for each CAN channel

Ą Extended operating temperature range from -40 to 85 °C (-40 to 185 °F)

CAN Interface for PC/104

The PCAN-PC/104 card enables the connection of one or two CAN networks to a PC/104 system. Multiple PCAN-PC/104 cards can easily be operated using interrupt sharing.

The card is available as a single- or dual-channel version. The opto-decoupled versions also guarantee galvanic isolation of up to 500 V between the PC and the CAN sides.

The package is also supplied with the CAN monitor PCAN-View for Windows and the programming interface PCAN-Basic.

PCAN-PC/104-Plus

FEATURES:

Ą Form factor PC/104

Ą Use of the 120-pin connection for the PCI bus

Ą Up to four cards can be used in one system

Ą 1 or 2 High-speed CAN channels (ISO 11898-2)

Ą Bit rates from 5 kbit/s up to 1 Mbit/s

Ą Compliant with CAN specifications 2.0A (11-bit ID) and 2.0B (29-bit ID)

Ą Connection to CAN bus through D-Sub slot bracket, 9-pin (in accordance with CiA® 303-1)

Ą NXP SJA1000 CAN controller, 16 MHz clock frequency

Ą NXP PCA82C251 CAN transceiver

Ą 5 V supply to the CAN connection can be connected through a solder jumper, e.g., for external bus converter

Ą Extended operating temperature range from -40 to 85 °C (-40 to 185 °F)

Ą Optionally available with galvanic isolation on the CAN connection up to 500 V, separate for each CAN channel

Ą PC/104-ISA stack-through connector

CAN Interface for PC/104-Plus

The PCAN-PC/104-Plus card enables the connection of one or two CAN networks to a PC/104-Plus system. Up to four cards can be operated, with each piggy-backing off the next. The CAN bus is connected using a 9-pin D-Sub plug on the slot bracket supplied.

The card is available as a single or dual-channel version. The opto-decoupled versions also guarantee galvanic isolation of up to 500 V between the PC and the CAN sides.

The package is also supplied with the CAN monitor PCAN-View for Windows and the programming interface PCAN-Basic.

Embedded Computing Design

Industrial Automation & Control PEAK-System Technik GmbH www.peak-system.com/quick/PC104-2 info@peak-system.com +49 (0) 6151-8173-20 www.linkedin.com/company/peak-system @PEAK_System

Industrial Automation & Control

PCAN-PC/104

GmbH

info@peak-system.com +49 (0) 6151-8173-20 www.linkedin.com/company/peak-system @PEAK_System

PEAK-System Technik

www.peak-system.com/quick/PC104-1

36 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

Ą Form factor PC/104

Ą Use of the 120-pin connection for the PCI bus

Ą Up to four cards can be used in one system

Ą 4 High-speed CAN channels (ISO 11898-2)

Ą Bit rates from 5 kbit/s up to 1 Mbit/s

Ą Compliant with CAN specifications 2.0A (11-bit ID) and 2.0B (29-bit ID)

Ą Connection to CAN bus through D-Sub slot brackets, 9-pin (in accordance with CiA® 303-1)

Ą FPGA implementation of the CAN controller (SJA1000 compatible)

Ą NXP PCA82C251 CAN transceiver

Ą Galvanic isolation on the CAN connection up to 500 V, separate for each CAN channel

Ą 5 V supply to the CAN connection can be connected through a solder jumper, e.g., for external bus converter

Ą Extended operating temperature range from -40 to 85 °C (-40 to 185 °F)

Technik

PCAN-PCI/104-Express

FEATURES:

Ą PCI/104-Express card, 1 lane (x1)

Ą Form factor PC/104

Ą Up to four cards can be used in one system

Ą 1 or 2 High-speed CAN channels (ISO 11898-2)

Ą Bit rates from 5 kbit/s up to 1 Mbit/s

Ą Compliant with CAN specifications 2.0A (11-bit ID) and 2.0B (29-bit ID)

Ą Connection to CAN bus through D-Sub slot bracket, 9-pin (in accordance with CiA® 303-1)

Ą FPGA implementation of the CAN controller (SJA1000 compatible)

Ą NXP PCA82C251 CAN transceiver

Ą Galvanic isolation on the CAN connection up to 500 V, separate for each CAN channel

Ą Supplied only via the 5 V line

Ą 5 V supply to the CAN connection can be connected through a solder jumper, e.g., for external bus converter

Ą Extended operating temperature range from -40 to 85 °C (-40 to 185 °F)

Ą Optionally available: PCI-104 stack-through connector

Four-Channel CAN Interface for PC/104-Plus

The PCAN-PC/104-Plus Quad card enables the connection of four CAN networks to a PC/104-Plus system. Up to four cards can be operated, with each piggy-backing off the next. The CAN bus is connected using a 9-pin D-Sub plug on the slot brackets supplied. There is galvanic isolation of up to 500 V between the computer and CAN sides.

The package is also supplied with the CAN monitor PCAN-View for Windows and the programming interface PCAN-Basic.

Industrial Automation & Control PEAK-System

CAN Interface for PCI/104-Express

The PCAN-PCI/104-Express card enables the connection of one or two CAN buses to a PCI/104-Express system. Up to four cards can be stacked together. The CAN bus is connected using a 9-pin D-Sub plug on the slot brackets supplied. There is galvanic isolation of up to 500 V between the computer and CAN sides.

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 37

Embedded Computing Design

The package is also supplied with the CAN monitor PCAN-View for Windows and the programming interface PCAN-Basic. Industrial Automation & Control PEAK-System Technik GmbH www.peak-system.com/quick/PC104-4 info@peak-system.com +49 (0) 6151-8173-20 www.linkedin.com/company/peak-system @PEAK_System

GmbH

info@peak-system.com +49 (0) 6151-8173-20 www.linkedin.com/company/peak-system @PEAK_System

PCAN-PC/104-Plus Quad

www.peak-system.com/quick/PC104-3

FEATURES:

Ą Optionally available: PC/104-ISA stack-through connector

PCAN-PCI/104-Express FD

FEATURES:

Ą PCI/104-Express card, 1 lane (x1)

Ą Form factor PC/104

Ą Up to four cards can be used in one system

Ą 1, 2, or 4 High-speed CAN channels (ISO 11898-2)

Ą Complies with CAN specifications 2.0 A/B and FD (ISO and Non-ISO)

Ą CAN FD bit rates for the data field (64 bytes max.) from 20 kbit/s up to 12 Mbit/s

Ą CAN bit rates from 20 kbit/s up to 1 Mbit/s

Ą Connection to CAN bus through D-Sub slot bracket, 9-pin (in accordance with CiA® 303-1)

Ą FPGA implementation of the CAN FD controller

Ą Microchip CAN transceiver MCP2558FD

Ą Galvanic isolation on the CAN connection up to 500 V, separate for each CAN channel

Ą CAN termination and 5 V supply to the CAN connection can be activated through a solder jumper

Ą Extended operating temperature range from -40 to 85 °C (-40 to 185 °F)

Ą Optionally available: PCI-104 stack-through connector

PEAK-System Technik GmbH

www.peak-system.com/quick/PC104-5

CAN FD Interface for PCI/104-Express

The PCAN-PCI/104-Express FD allows the connection of PCI/104Express systems to CAN and CAN FD buses. Up to four cards can be stacked together. The CAN bus is connected via 9-pin D-Sub connectors to the supplied slot brackets. There is a galvanic isolation between the computer and the CAN side up to 500 V. The card is available in single-, dual-, or four-channel versions. The monitor software PCAN-View and the programming interface PCAN-Basic are included in the scope of supply and support the new standard CAN FD.

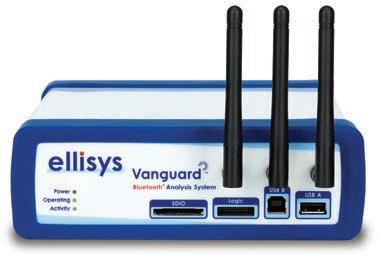

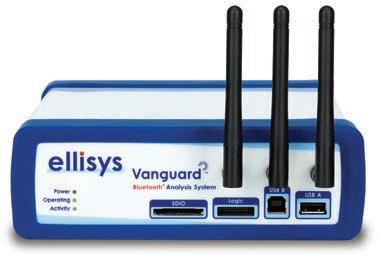

Advanced Wireless Protocol Analysis System

Advanced Wireless Protocol Analysis System The most advanced, most comprehensive Bluetooth protocol analyzer ever made. Building on a legacy of innovation, the Bluetooth Vanguard All-In-One Wireless Protocol Analysis System delivers new advances designed to ease the increasingly complex tasks of Bluetooth developers.

With its revolutionary wideband Digital Radio and integrated Allin-One hardware approach, Ellisys has changed the way Bluetooth protocol capture and analysis is done, by radically overcoming the drawbacks of legacy approaches. The Ellisys wideband capture approach robustly records any packet, at any time, from any neighboring piconet, with zero-configuration and without being intrusive. Vanguard provides synchronized capture and analysis of BR/EDR, Bluetooth Low Energy, Wi-Fi 802.11 a/b/g/n/ac (3x3), WPAN 802.15.4 (all 16 2.4 GHz channels), raw 2.4 GHz RF spectrum analysis, HCI (USB, UART, SPI), generic SPI/UART/I2C/SWD communications, WCI-2, logic signals, and Audio I2S.

FEATURES

Ą All-in-One: Fully hardware-integrated, time-synchronized, and truly one-click concurrent capture of BR/EDR, Bluetooth Low Energy, Wi-Fi, WPAN (IEEE 802.15.4), raw RF spectrum, HCI, logic/GPIO, generic I2C, UART, SWD, and SPI, Audio I2S, and WCI-2

Ą Bluetooth Wideband Capture: Easy and rock-solid capture of any traffic on all channels

Ą Wi-Fi 802.11 a/b/g/n/ac (3x3) Capture: Extremely accurate and perfectly synchronized Wi-Fi capture accelerated by Ellisys hardware

Ą WPAN 802.15.4 Wideband Capture: Concurrent capture of all 16 WPAN 2.4 GHz channels for an unmatched coexistence analysis capability

Ą Connection / Power Flexibility: Connect, control, and power the system locally or remotely via networkable GbE or USB 3.1 over Type-C™

Ą Advanced Features for Bluetooth LE Audio

https://ellisys.com/products/bv1

Embedded Computing Design

Industrial Automation & Control

info@peak-system.com +49 (0) 6151-8173-20 www.linkedin.com/company/peak-system @PEAK_System

Ellisys www.ellisys.com sales.usa@ellisys.com 866-724-9185 @Ellisys1

www.linkedin.com/company/ellisys

Ellisys Bluetooth® Vanguard™

Wireless

38 Embedded Computing Design EMBEDDED WORLD | Spring 2023 www.embeddedcomputing.com

SYN4778: Lowest Power, Smallest, Most Accurate GNSS IC for IoT Devices

The SYN4778 is the smallest, lowest power, most accurate Global Navigation Satellite System (GNSS) IC for the Internet of Things (IoT). The chip draws 80% less power and comes in a package that is 30% smaller than comparable devices while providing a 50% improvement in accuracy. It extends battery life, reduces product size, and enhances the performance of advanced location-based services (LBSs) for IoT devices such as wearables, as well as mobile accessories, asset tags, tracking systems, drones, and navigation systems.

The GNSS receiver typically consumes an out-sized portion of available power in battery-powered IoT devices. The SYN4778’s advanced 7-nm semiconductor process and on-chip power management greatly reduce this power draw. In addition, the chip uses both the L1 and L5 satellite bands to reduce the time to first fix (TTFF) by 35% and the power consumed for first fix by 72%. Fast, low-power TTFF greatly improves the end-user experience, while lower overall power and smaller footprint give product developers the ability to extend battery life and shrink the overall product size.

Alternatively, developers can add more device functionality and features – such as biometrics, movement, or ambient sensors – for a given product power budget and form factor. To enhance location accuracy, the SYN4778 uses a proprietary satellite tracking database.

FEATURES

Ą The SYN4778’s advanced 7-nm semiconductor process and on-chip power management greatly reduce power consumption

Ą Uses both the L1 and L5 satellite bands to reduce the time to first fix (TTFF) by 35% and the power consumed for first fix by 72%

Ą Uses proprietary satellite tracking database to enhance accuracy

Ą Measures 2.4 x 2.7 mm (40-ball FCBGA package)

Ą Option to add more device functionality and features – such as biometrics, movement, or ambient sensors – for a given product power budget and form factor

Ą Advanced multipath interference mitigation using L5 band signals from GPS, Galileo, BeiDou, NAVIC, SBAS, and Quasi Zenith Satellite Systems (QZSS)

Ą LTE jamming and signal filtering, and continuous – highly parallel – search and track of the complete GNSS channels (including the L5 band) for greater positioning accuracy for LBS applications, particularly in urban environments

Ą Support for multiple operating systems (such as Android, Linux, and FreeRTOS) and third-party software to enable a broader range of application-optimized IoT devices

Ą Low-noise, high-linearity RF front end makes an external LNA and second SAW filter optional to reduce BOM and increase layout flexibility

Embedded Computing Design

IoT

Synaptics Incorporated www.synaptics.com sales@synaptics.com www.synaptics.com/contact www.linkedin.com/company/synaptics @ SynaCorp

www.synaptics.com

www.embeddedcomputing.com Embedded Computing Design EMBEDDED WORLD | Spring 2023 39

Our batteries offer a winning combination: a patented hybrid layer capacitor (HLC) that delivers the high pulses required for two-way wireless communications; the widest temperature range of all; and the lowest self-discharge rate (0.7% per year), enabling our cells to last up to 4 times longer than the competition.

Looking to have your remote wireless device complete a 40-year marathon? Then team up with Tadiran batteries that last a lifetime.

Tadiran Batteries 2001 Marcus Ave. Suite 125E Lake Success, NY 11042 1-800-537-1368 516-621-4980 www.tadiranbat.com PROVEN 40 YEAR OPERATING LIFE *

Remote wireless devices connected to the Industrial Internet of Things (IIoT) run on Tadiran bobbin-type LiSOCl2 batteries.

* Tadiran LiSOCL2 batteries feature the lowest annual self-discharge rate of any competitive battery, less than 1% per year, enabling these batteries to operate over 40 years depending on device operating usage. However, this is not an expressed or implied warranty, as each application differs in terms of annual energy consumption and/or operating environment.

run longer on Tadiran batteries. ANNUAL SELF-DISCHARGE TADIRAN 0.7% Up to 3% COMPETITORS

IIoT devices

By Mark Pitchford, LDRA

By Mark Pitchford, LDRA